CoE 197U Two-Stage MOS Operational Transconductance Amplifiers

If a larger gain than that of a differential amplifier is needed, the next step is to use cascade amplifier stage/s or cascode the differential pair. Cascoding uses common-gate amplifiers/buffers to increase gain at the cost of reduced voltage swing. Meanwhile, cascading can achieve larger voltage swings but need separate current paths and therefore, consume more power. With nominal supply voltages decreasing with technology, cascoding becomes less viable. In this lecture, we will look at a typical 2-stage MOS amplifier.

The main reference for this topic is chapter 6.3 of the Analysis and Design of Analog Integrated Circuits book[1].

Contents

Op-amps and OTA

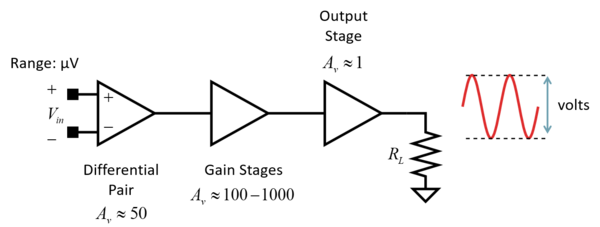

An operational amplifier or op-amp can be roughly divided into three stages (Fig. 1): the differential pair, the gain stage/s, and the output stage. The differential pair enables the op-amp to have a differential input, have a large input resistance, and provide some gain. The gain stage/s provide the additional gain needed, but in doing so, end up with a large output resistance that cannot drive heavy (low resistance) resistive loads. The output stage provides a gain of 1 or less. It is added to give the op-amp low output resistance, large output swing, and the ability to provide large output currents.

The differential and gain stages combined can be viewed as an OTA or operational transconductance amplifier. Thus, the op-amp can be viewed as an OTA with an output buffer (Fig. 2). OTAs have large gain and large output resistance. An OTA produces an output current from an input voltage and can drive capacitive loads (provide charging current) which are common in on-chip loads (e.g. gate of another MOSFET). A low output resistance is not necessarily required in driving capacitive loads.

Miller OTA

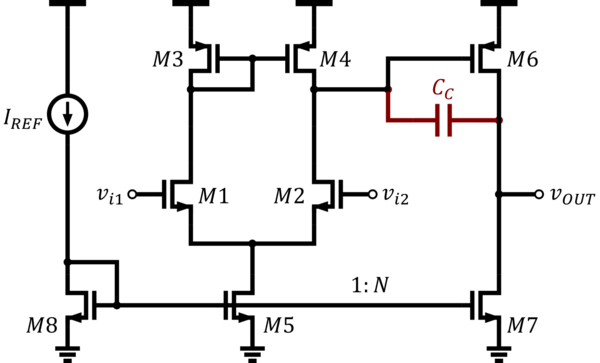

The Miller OTA is a simple 2-stage OTA composed of a current mirror-loaded differential pair stage and a common source stage (Fig. 3). It is one of the go-to amplifiers in IC design because of its simplicity. The topology contains only a few transistors, making it relatively easy to design. The circuit also has a simple biasing scheme. The design of the current source itself is a different story! However, in less critical applications, a resistor can be used in place of the current source. There are many problems associated with the latter scheme. On-chip resistors are not accurate, may occupy large chip area, can change resistance with temperature, and provides current that is sensitive to temperature and supply voltage changes.

This two-stage OTA can be compensated by using a Miller compensating capacitor, . Compensation is needed to ensure that the amplifier is stable when used in feedback. You may refer to these materials[2] to review the fundamental concepts of feedback and compensation although the Miller compensation is covered only on Lec 12B. If the load capacitance is not large enough to create a dominant pole, then the capacitor can be added. Placing a very large capacitor to produce a dominant pole is expensive in terms of chip area. By placing the capacitor as shown, a smaller capacitance value (and thus area) is needed since the Miller effect amplifies the capacitance by a factor . This amplified capacitance effectively appears at the input of the common source stage (or output of the differential pair) to ground. With a large enough , the pole associated with the output of the differential pair can be made dominant to ensure stability.

Before proceeding, note that the analysis to be presented assumes that all transistors are saturated square law devices described by the equations below (for NMOS). The term overdrive voltage or is used to refer to or . For PMOS devices, refers to . The paired devices (M1 and M2, and M3 and M4) have the same dimensions. All NMOS transistors are also assumed to have the same threshold voltage while all PMOS transistors are assumed to have the same threshold voltage .

AC Analysis (Low Frequency)

The AC characteristics will be discussed first to evaluate the impact of design decisions done when sizing and biasing the transistors at DC. Only very low frequencies are considered such that the capacitor is still open and can be disregarded.

Gain

The input resistance of the 2nd stage, the common source stage, is infinite. Thus, there will be no loading between the two stages. The overall low-frequency small-signal gain of the Miller OTA is simply . From the differential pair discussion , it was shown that the gain of an NMOS-input differential pair is some . Meanwhile, the gain of a PMOS common source amplifier with an NMOS active load is some .

-

(1)

-

The differential pair stage’s gain is non-inverting since the negative terminal of the input is at the output side. On the other hand, the common source stage is inverting. The overall gain of the two-stage OTA is inverting. If a non-inverting gain is desired, the input connection can just be switched (positive terminal of the input at M2 gate instead). It can also be said that the gain is related to some quantity.

Output Resistance

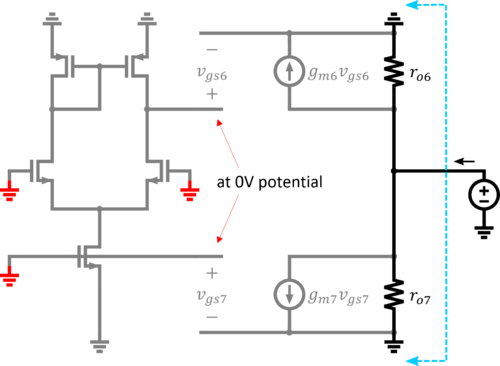

The output resistance can be determined by grounding the input and placing a test source at the output. Since the input to the differential pair is zero, its output must also be zero. Since the source of M6 is also grounded, then . At the bottom, the gate of M7 is connected to some DC bias which is an AC ground. Since the source of M7 is also grounded, then . With the help of Fig. 4, it is easy to see that the output impedance is just and in parallel.

-

(2)

-

Transconductance

From the overall gain (Eq. 1) and output resistance (Eq. 2), it can be inferred from that

-

(3)

-

Input Resistance

The input resistance of the OTA is the input resistance of the differential pair which is also infinite.

-

(4)

-

Discussion

The output impedance can be expressed in terms of and . M6 and M7 share the same branch current (i.e. ). However, the for M6 and M7 are not necessarily the same.

The gain expression can be expanded in the same fashion and using . Note also that .

-

(5)

-

The terms are dictated by the technology or process. can be decreased to improve gain by increasing the transistor lengths (i.e. less channel length modulation). On the other hand, is a design choice on how to bias the transistors at DC. Decreasing increases the gain. However, decreasing operates the transistor closer to moderate or weak inversion where the transistor (transit frequency) is lower. The same is true when increasing the channel length. Thus, while increasing the length and/or decreasing improves the gain, the frequency response of the transistor and of the amplifier is degraded. Note that increasing the current by increasing the transistor widths (but maintaining ) will not increase the gain but will increase the bandwidth (as long as the parasitic capacitances are much smaller than the load capacitance) at the cost of area and power. These observations are generally true with amplifiers whose gain is based on or the transistor’s intrinsic gain.

DC Analysis

Since there is no current through the gate of M6, then the two stages can be discussed separately. The differential pair has been analyzed in detail here . If the transistors are perfectly matched, then and . This means that the drain nodes of M1-4 must be at the same potential. The output of the differential pair or the drain of M4 must be at . This voltage is the gate voltage seen by M6. Thus, M3, M4, and M5 must have the same gate-to-source voltages.

With the earlier mentioned assumption that the of all PMOS devices are the same, then the of transistors M3, M4, and M6 must be the same. In process technologies or sizes where the threshold voltage is dependent on the device length, the assumption will only be true if . Aside from that, using equal device lengths will make layout easier and help match these transistors.

To make sure that the transistors on the 2nd stage are saturated, the M6 and M7 must be sized and biased for the same drain current (i.e. ). While the of M6 is dictated by the of M3 and M4, the of M7 and M5 is dictated by the of M8. Again, this assumes that for M5, M7, and M8 are the same, and using helps achieve this.

Fig. 3 shows that the dimensions of M5 and M7 are related by a proportion of (i.e. M7’s width-to-length ratio is N times larger than that of M5). Since the transistors have the same , then the constant can be also used to refer to the ratio of drain currents assuming the effect of CLM is negligible.

At DC, half of the tail current flows through M3 and M4 (i.e. ). Thus, the sizes of M4 and M5 must be related by a proportion of .

Thus, for example, if or , then M6 must be as large as M4.

Effects of Mismatch

Assume that all transistors that must be matched are perfectly matched, except possibly M1 and M2. Let where only when M1 and M2 are perfectly matched. By KCL, this means that as well, even though M3 and M4 are perfectly matched. Note that still, since their gates and sources are shorted. Thus, since M3 and M4 are matched (, , , etc.), the only way for their currents to be different is by having different drain-source voltages. Let .

-

(6)

-

Suppose the circuit is designed for 1V supply, . The output of the differential pair stage will ideally be at 0.6V. Suppose that and that M1 and M2 were mismatched such that . By KCL, which means that will be slightly off from . However, assume that the change is small enough such that stays approximately at 0.4V. By Eq. 6, it can be shown that will tend to be at 1.414V. This of course cannot happen since the supply is only 1V. However, this suggests that the output will rail, and the transistors will not anymore be saturated even if , which is just off by 0.01 from the ideal case of 1.

Another way of looking at the mismatch problem is by lumping the effects of mismatch and referring them into the input, also called the input-referred offset voltage. The input-referred offset voltage caused by mismatch from the differential pair stage can be shown to follow Eq. 7.

-

(7)

-

The first 2 terms are caused by difference () in threshold voltages of M1 and M2, and M3 and M4, respectively. The effect of the second term can be reduced by making . This can be done by sizing the W/L ratio of M3 and M4 to be smaller than that of M1 and M2 since . Alternatively, which means that the second term can be reduced by using a larger overdrive voltage for the current mirror-load compared to the differential pair. The third term is caused by mismatches in device dimensions. The effect of this term can be reduced by making the transistors themselves large, such that minor differences in size due to etching imperfections will be relatively small or negligible. The effect can also be reduced by operating the input transistors with a low overdrive voltage.

This input-referred offset adds to the actual input. If there is no input yet, the offset remains and is amplified at the output. That is why in the analysis with , the output still railed because of the gain of the amplifier. Note also that the change in the output of the differential pair will also be amplified by the common source stage so the offset’s effect at the actual output will be larger.

![{\displaystyle V_{offset,i}\cong \Delta V_{TH\left(1-2\right)}+\Delta V_{TH\left(3-4\right)}{\frac {g_{m3}}{g_{m1}}}+{\frac {\Delta V_{OV\left(1-2\right)}}{2}}\left[{\frac {\Delta \left({\frac {W}{L}}\right)_{\left(3-4\right)}}{\left({\frac {W}{L}}\right)_{\left(3-4\right)}}}-{\frac {\Delta \left({\frac {W}{L}}\right)_{\left(1-2\right)}}{\left({\frac {W}{L}}\right)_{\left(1-2\right)}}}\right]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/920c86ebbfffa0d1c28f6b439b9d66c07b0c9945)