CoE 197U Scaling

Contents

Moore's Law

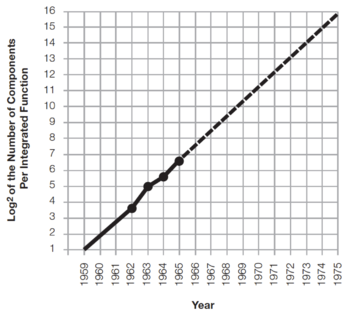

In 1965, Gordon Moore published a 4-page paper entitled "Cramming more components onto integrated circuits"[1], where he predicted that the number of components in an integrated circuit will increase by a factor of two every year, as shown in Fig. 1. Note that he based his extrapolation on just 4 data points!

Figure 1: Gordon Moore's 1965 prediction[1]. |

Why is this paper and the graph in Fig. 1 important? Gordon Moore's prediction, also known as Moore's Law, has reflected and, more importantly, driven the steady and rapid progress in computing technology[2]. Thus, satisfying Moore's Law has become the goal instead of being merely a prediction.

Evolution of Complexity

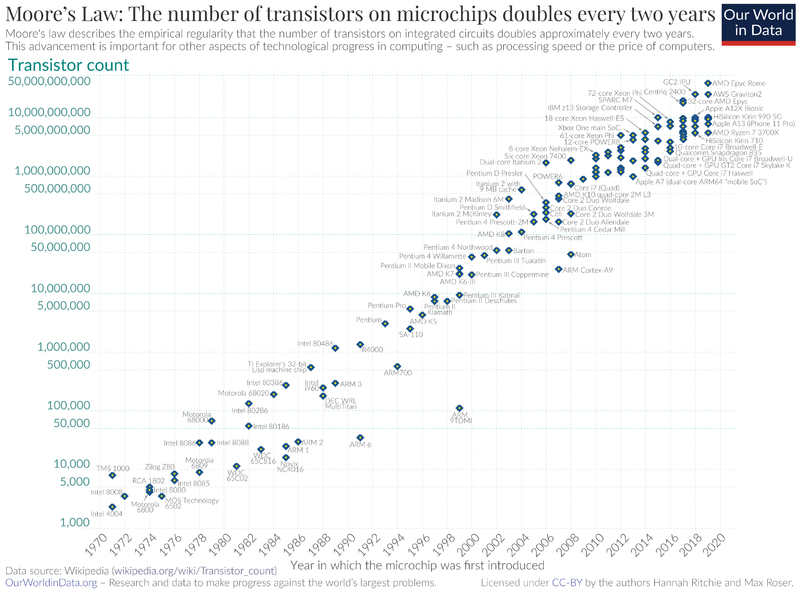

As Gordon Moore predicted, the cost and performance advantage of putting more and more devices into a single integrated circuit (IC) led to the rapid increase in circuit complexity. One convenient indicator of circuit complexity is the number of transistors contained in a single IC, reaching the 1-billion transistor level in 2010, and achieving almost 50 billion transistors in 2020, as shown in Fig. 2.

Figure 2: Transistor Count (1970 - 2020)[3]. |

For more than 30 years, the development of integrated circuits continued roughly on the trajectory predicted by Moore's Law.

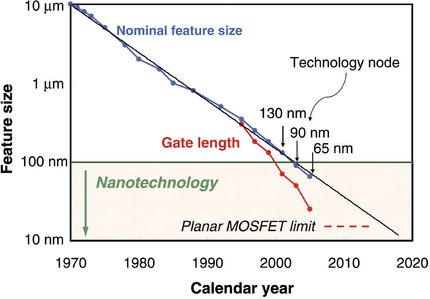

Figure 3: Technology node and transistor gate length versus calendar year[4]. |

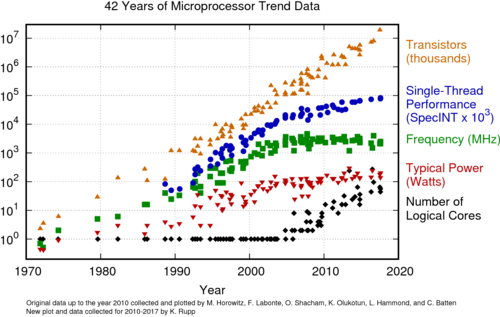

Figure 4: Scaling and processor performance[5]. |

Challenges in Digital Design

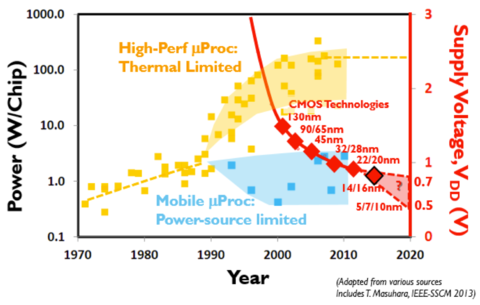

Figure 5: Supply voltage and power scaling[6]. |

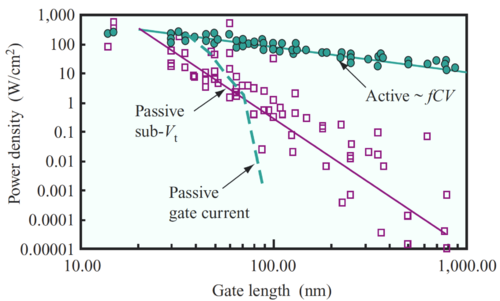

Figure 6: Active and Leakage Power[7]. |

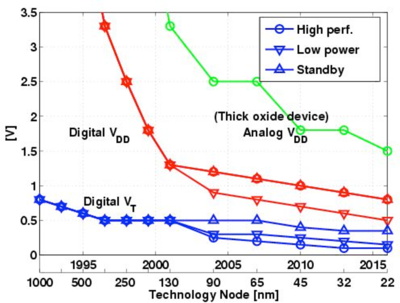

Figure 7: Supply and threshold voltage scaling[8]. |

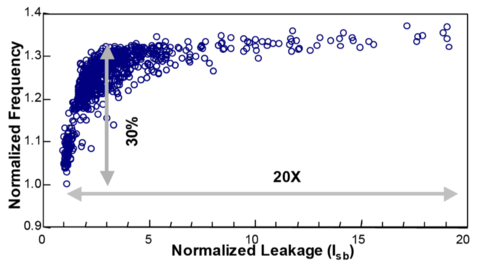

Figure 8: Leakage and frequency variations[9]. |

Why Scale?

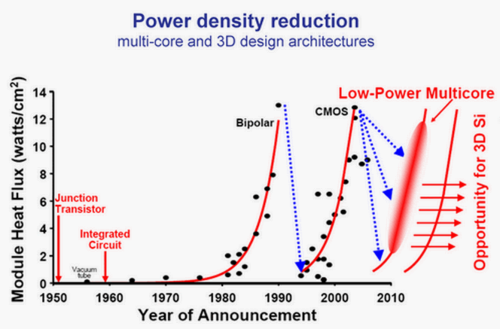

Figure 9: Semiconductor power density[10]. |

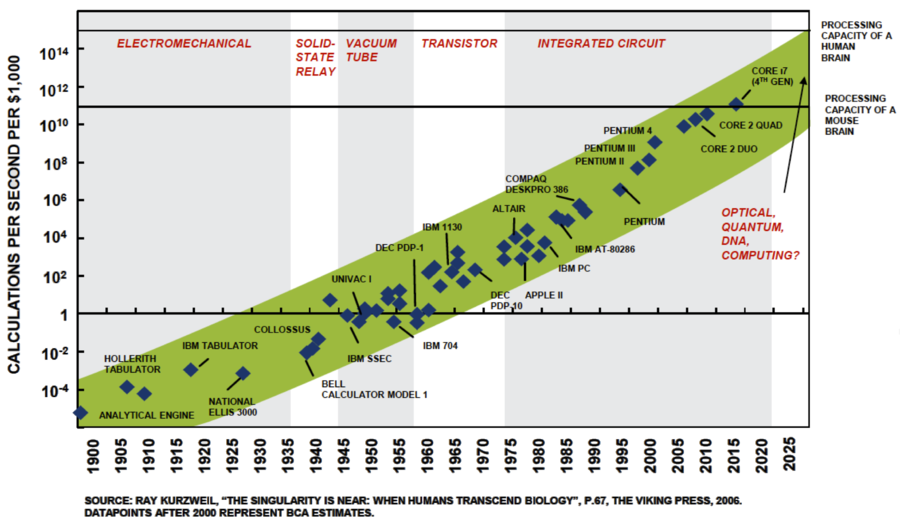

Figure 10: Calculations per second for a fixed cost[11]. |

The Cost of Integrated Circuits

Cost is the main motivation for reducing device sizes. Aside from the marked improvement in speed, more transistors can be integrated in the same die or wafer, and this results in the significant reduction in the cost per transistor. The total cost of producing an integrated circuit can be broken down into two components: (1) the fixed or non-recurrent engineering costs (NRE), and (2) the variable or recurrent costs.

- Non-Recurrent Engineering (NRE) Costs

-

- NRE costs are overhead costs independent of volume, i.e. the number of integrated circuits made or sold.

- Examples of NRE costs include design time and manpower, CAD tools and equipment, mask generation costs, etc.

- Recurrent Costs

-

- Costs that are proportional to the volume of ICs produced.

- This includes the fabrication costs, packaging costs, and testing costs.

- In most cases, these costs are proportional the chip area.

Thus, the cost of an integrated circuit can be expressed as:

-

(1)

-

Where the components of the variable cost are:

-

(2)

-

Die Cost

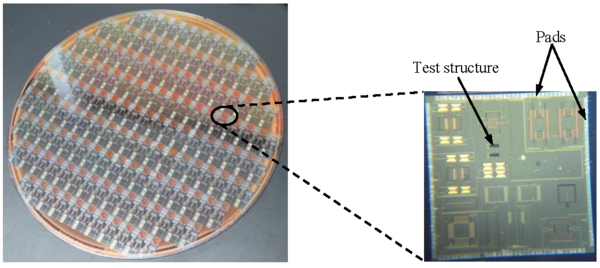

The cost of a die or chip is dependent on the (1) cost of a wafer, (2) the number of chips in a wafer, and (3) the die yield.

Yield

References

- ↑ 1.0 1.1 Gordon E Moore, Cramming more components onto integrated circuits, Electronics, Volume 38, Number 8, April 19, 1965 (pdf)

- ↑ Gordon Moore: The Man Whose Name Means Progress, IEEE Spectrum, March 2015.

- ↑ Wikimedia

- ↑ S. E. Thompson, S. Parthasarathy, Moore's law: the future of Si microelectronics, Materials Today, Volume 9, Issue 6, 2006, Pages 20-25. (link)

- ↑ K. Rupp, 42 Years of Microprocessor Trend Data, https://www.karlrupp.net/2018/02/42-years-of-microprocessor-trend-data/

- ↑ B. Kunert, Integration and Application of Epitaxial Systems: III/V on Silicon for Optoelectronics, IMEC Belgium 2015

- ↑ W. Haensch et al., Silicon CMOS devices beyond scaling, IBM Journal of Research and Development, vol. 50, no. 4.5, pp. 339-361, July 2006, doi: 10.1147/rd.504.0339.

- ↑ ITRS, The International Technology Roadmap for Semiconductors (2004 edition), 2004. Technical Report, http://public.itrs.net

- ↑ S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi and V. De, Parameter variations and impact on circuits and microarchitecture, Proceedings 2003. Design Automation Conference (IEEE Cat. No.03CH37451), Anaheim, CA, USA, 2003, pp. 338-342, doi: 10.1145/775832.775920.

- ↑ Chen (IBM), ISS Europe 2007, (link).

- ↑ BCA Research (link).

- ↑ J. Dennis, CMOS Compatible Bulk Micromachining, IntechOpen 2013 (link)