Passive CMOS Devices

Passive devices such as resistors, capacitors, and inductors, are commonly used in biasing circuits, feedback networks, and signal or energy storage blocks. However, these passive devices, when built on fabrication processes that are optimized for transistors, may have characteristics different from their ideal or discrete counterparts. In this module, we examine the behavior of passive devices built alongside CMOS transistors.

Contents

Resistors

In standard digital CMOS processes, there is usually no provision for high resistance layers, since resistances are typically deemed bad for digital circuits. But in analog design, we often need well-controlled resistors, with relatively large resistance values.

Sheet Resistance

In order to evaluate if a particular layer could be used as to build a resistor, we look to their sheet resistance. Recall that for a resistor:

-

(1)

-

Where is the sheet resistance of the layer, is the resistivity of the material, is the length along the direction of the current, and , is the cross sectional area normal to the current flow, which is equal to the product of the layer thickness, and is the width of the layer perpendicular to the current flow.

Note that the units of sheet resistance is since is the resistance of a square, i.e. when . Table 1 shows indicative sheet resistance values of the common conductive layers in a CMOS process:

| Layer | Sheet Resistance |

|---|---|

| Metal | |

| Polysilicon | |

| or Diffusion | |

| -well |

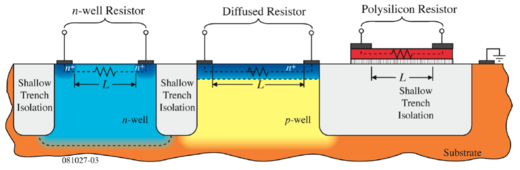

An illustrative cross-section of resistors using these layers are shown in Figs. 1 and 2.

Figure 1: Resistors built using semiconductor layers[1]. |

Figure 2: Resistors built using metal layers[1]. |

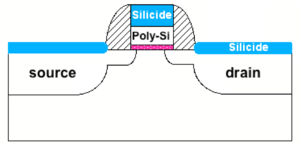

In a CMOS process optimized for digital circuits, the low sheet resistances of the semiconductor layers are due to a low-resistance silicide layer deposited on top of the semiconductor layer, as shown in Fig. 3. In analog CMOS processes, we are usually given the option to place a silicide block, i.e. to prevent the silicide layer from being deposited on specific locations on the die. Table 2 contains illustrative values of the sheet resistance of the semiconductor layers with the silicide block option.

| Layer | Sheet Resistance | |||

|---|---|---|---|---|

| -polysilicon | ||||

| -polysilicon | ||||

| -diffusion | ||||

| -diffusion | ||||

| -well |

Note that the non-silicided layers have significantly larger sheet resistances.

Temperature and Voltage Coefficients

In general, semiconductor resistor values change with temperature and applied voltage, and to describe these changes, we use temperature and voltage coefficients:

-

(2)

-

Where is the nominal resistance value at some reference temperature , is the temperature coefficient, is the voltage coefficient, is the body voltage coefficient, and are the terminal voltages, and is the bulk or body voltage.

In semiconductors, we know that the resistivity is a strong function of temperature, roughly due to two mechanisms:

- Increasing the temperature increases the number of free carriers, thus lowering the resistance, resulting in negative temperature coefficients.

- This increase in free carriers increases the probability of scattering events or collisions, increasing the effective resistance, resulting in positive temperature coefficients.

![{\displaystyle T_{C}\,\mathrm {[ppm/^{\circ }C]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/04b91e8231c6b3dfb9f275182a37fa14a115d0b4)

![{\displaystyle V_{C}\,\mathrm {[ppm/V]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/2999d120b9c9f1a9b2dffbdfb528de8b30f600a1)

![{\displaystyle B_{C}\,\mathrm {[ppm/V]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/4c9b77494824b8b10e640e2a1c937739746f56ee)

![{\displaystyle R=R_{0}\left[1+T_{C}\left(T-T_{0}\right)+V_{C}\left(V_{1}-V_{2}\right)+B_{C}\left({\frac {V_{1}+V_{2}}{2}}-V_{B}\right)\right]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/4dcca9bfc0e25a572af319c1d76b0f841419492f)