CoE 197U The CMOS Inverter

Contents

The Inverter Voltage Transfer Characteristics (VTC)

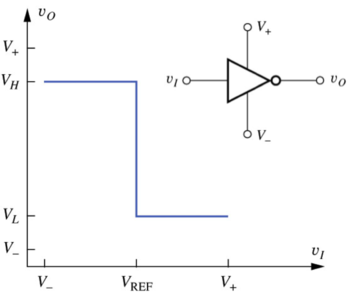

The Ideal Inverter VTC

Figure : The ideal inverter voltage transfer characteristic (VTC)[1]. |

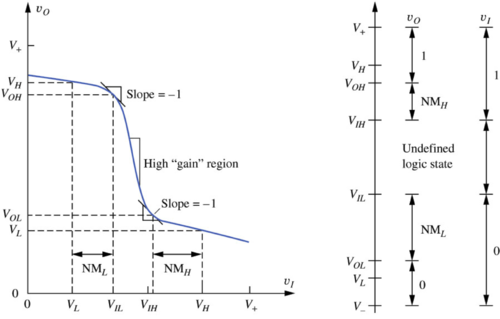

Static Design Metrics

Figure : The non-ideal inverter voltage transfer characteristic (VTC)[1]. |

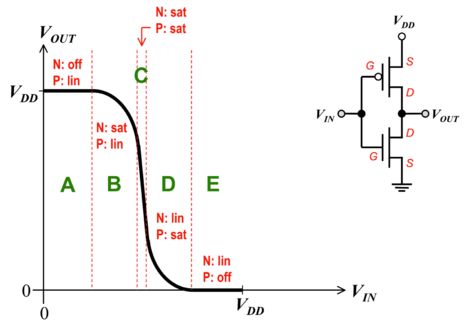

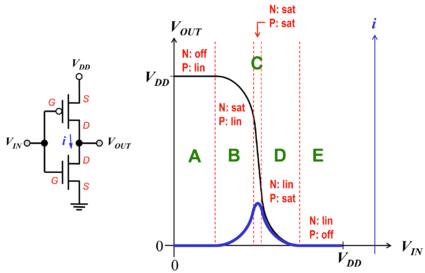

Figure : The CMOS inverter voltage transfer characteristic (VTC)[2]. |

Noise in Digital Circuits

Noise Rejection

Noise Margins

The Regenerative Property of Inverters

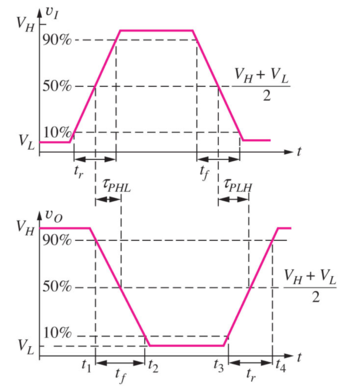

Inverter Delay

Figure: Logic delay definitions [1]. |

Power Dissipation

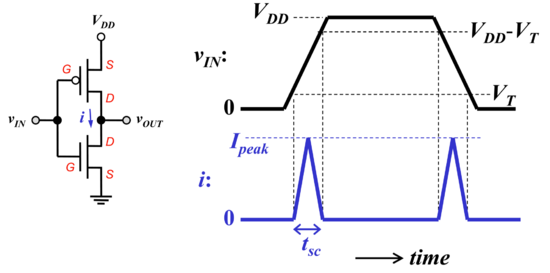

Figure : The CMOS switching current[3]. |

Figure : The CMOS transient power dissipation[3]. |