Difference between revisions of "CoE 197U The CMOS Inverter"

| Line 19: | Line 19: | ||

{| | {| | ||

|[[File:Ideal inverter vtc.png|thumb|350px|Figure 1: The ideal inverter voltage transfer characteristic (VTC)<ref name="wu2014">Ming Wu's UCB EE105 (Fall 2014) Lecture 24 Slides ([https://inst.eecs.berkeley.edu/~ee105/fa14/lectures/Lecture24-Digital%20Circuits-CMOS%20Inverters.pdf link])</ref>.]] | |[[File:Ideal inverter vtc.png|thumb|350px|Figure 1: The ideal inverter voltage transfer characteristic (VTC)<ref name="wu2014">Ming Wu's UCB EE105 (Fall 2014) Lecture 24 Slides ([https://inst.eecs.berkeley.edu/~ee105/fa14/lectures/Lecture24-Digital%20Circuits-CMOS%20Inverters.pdf link])</ref>.]] | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | One implementation of the inverter is to use a single NMOS transistor and a resistor, as shown in Fig. 2. Using our switch model for the NMOS transistor, we can see that when the input is low or at logic '''0''', the output is pulled up to <math>V_{DD}</math> since the switch is open. When the input voltage is equal to <math>V_{DD}</math>, the switch is closed and the output is pulled down close to ground. For a finite on switch resistance, <math>R_{ON}</math>, the output voltage becomes: | ||

| + | |||

| + | {{NumBlk|::|<math> | ||

| + | v_O = \frac{R_{ON}}{R_{ON} + R}\cdot V_{DD} | ||

| + | </math>|{{EquationRef|2}}}} | ||

| + | |||

| + | {| | ||

| + | |[[File:Nmos inverter.png|thumb|400px|Figure 2: The NMOS inverter.]] | ||

| + | |[[File:Cmos inverter.png|thumb|400px|Figure 3: The CMOS inverter.]] | ||

|- | |- | ||

|} | |} | ||

== Static Design Metrics == | == Static Design Metrics == | ||

| + | In real inverters, the VTC can deviate from the ideal | ||

{| | {| | ||

Revision as of 13:21, 10 March 2021

To understand the analysis and design of digital circuits, we will look at its fundamental element -- the digital gate. We will start with the simplest digital gate, the inverter.

Contents

The Inverter Voltage Transfer Characteristics (VTC)

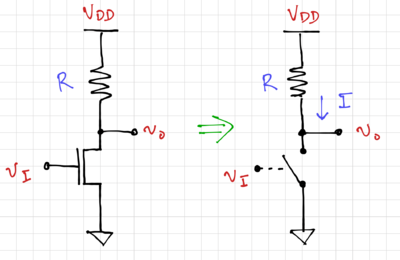

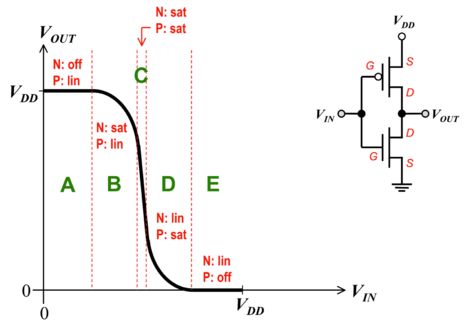

The functionality of the inverter can be captured by looking at the output voltage as we change the input voltage, or the voltage-transfer characteristic (VTC).

The Ideal Inverter VTC

Let us define an ideal inverter, where:

-

(1)

-

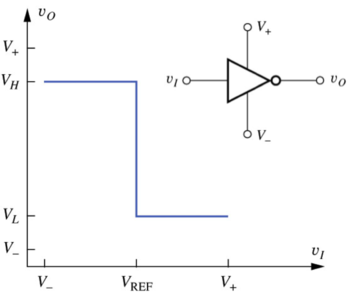

Where is logic 1 voltage level, and in general may or may not be equal to the positive supply voltage, , and is logic 0 voltage level, and in general may or may not be equal to the negative supply voltage, . The VTC of this ideal inverter, as well as the standard inverter circuit symbol, is shown in Fig. 1.

Figure 1: The ideal inverter voltage transfer characteristic (VTC)[1]. |

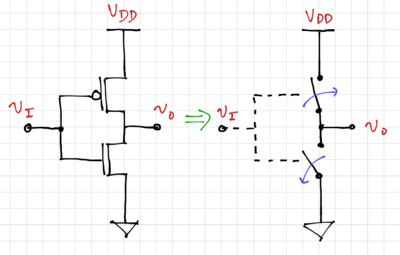

One implementation of the inverter is to use a single NMOS transistor and a resistor, as shown in Fig. 2. Using our switch model for the NMOS transistor, we can see that when the input is low or at logic 0, the output is pulled up to since the switch is open. When the input voltage is equal to , the switch is closed and the output is pulled down close to ground. For a finite on switch resistance, , the output voltage becomes:

-

(2)

-

Static Design Metrics

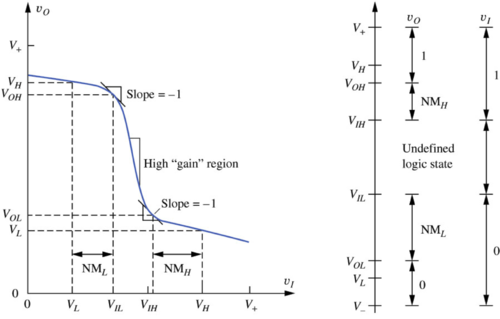

In real inverters, the VTC can deviate from the ideal

Figure : The non-ideal inverter voltage transfer characteristic (VTC)[1]. |

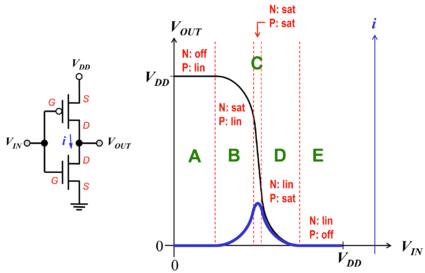

Figure : The CMOS inverter voltage transfer characteristic (VTC)[2]. |

Noise in Digital Circuits

Noise Rejection

Noise Margins

The Regenerative Property of Inverters

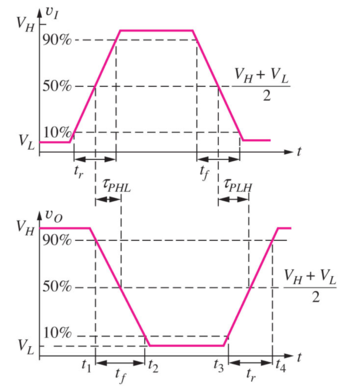

Inverter Delay

Figure: Logic delay definitions [1]. |

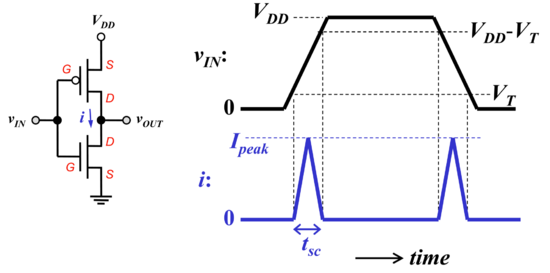

Power Dissipation

Figure : The CMOS switching current[3]. |

Figure : The CMOS transient power dissipation[3]. |