Difference between revisions of "CoE 197U The MOS Switch"

Jump to navigation

Jump to search

| Line 1: | Line 1: | ||

== Levels of Abstraction == | == Levels of Abstraction == | ||

| + | As integrated circuits continue to increase in complexity and sophistication, the amount of information and information processing needed to design, fabricate, and test these ICs also increase. Without a way to organize this information, engineers can be easily overwhelmed. One strategy is to define levels of abstraction, where we partition the information, and use only the components needed for a particular task. This strategy can then be used to create models appropriate for a certain objective. | ||

| + | |||

| + | We create models to allow us to predict the behavior of a circuit or system. | ||

| + | |||

| + | |||

{| | {| | ||

|[[File:Levels of abstraction.png|thumb|800px|Figure 1: Levels of abstraction<ref name="ghosh2020">A. Ghosh, Fault Modeling in Chip Design - VLSI DFT, 2020 ([https://technobyte.org/fault-modeling-models-vlsi-dft/ link])</ref>.]] | |[[File:Levels of abstraction.png|thumb|800px|Figure 1: Levels of abstraction<ref name="ghosh2020">A. Ghosh, Fault Modeling in Chip Design - VLSI DFT, 2020 ([https://technobyte.org/fault-modeling-models-vlsi-dft/ link])</ref>.]] | ||

Revision as of 10:18, 8 March 2021

Contents

Levels of Abstraction

As integrated circuits continue to increase in complexity and sophistication, the amount of information and information processing needed to design, fabricate, and test these ICs also increase. Without a way to organize this information, engineers can be easily overwhelmed. One strategy is to define levels of abstraction, where we partition the information, and use only the components needed for a particular task. This strategy can then be used to create models appropriate for a certain objective.

We create models to allow us to predict the behavior of a circuit or system.

Figure 1: Levels of abstraction[1]. |

What is a Transistor?

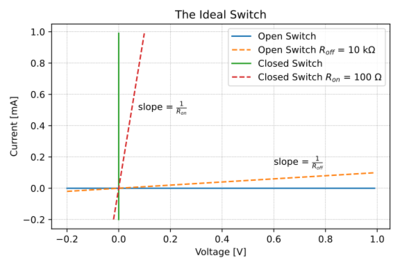

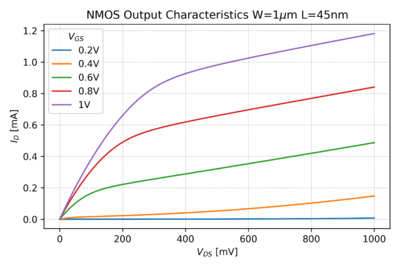

Figure 2: The 45nm NMOS PTM[2] output characteristics. |