Difference between revisions of "CoE 197U IC Fabrication"

| Line 26: | Line 26: | ||

Proceed to the next module: [[CoE 197U Scaling | Scaling]] | Proceed to the next module: [[CoE 197U Scaling | Scaling]] | ||

| − | |||

| − | |||

== References == | == References == | ||

<references /> | <references /> | ||

Revision as of 15:03, 1 March 2021

CMOS Technology Review

Knowing how integrated devices are fabricated, and how the fabrication process affects the characteristics and performance of these devices, is one of the pillars of good analog and digital circuit design. In this module, we are interested in the relationships between the fabrication process steps and parameters to the device characteristics and performance.

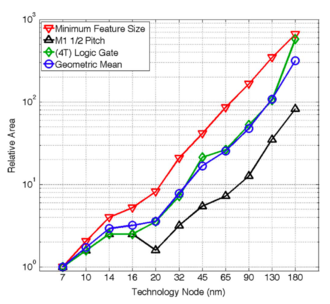

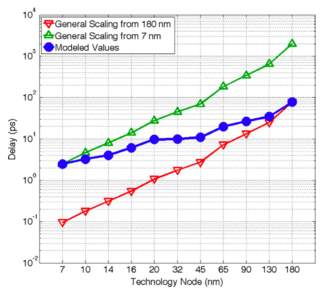

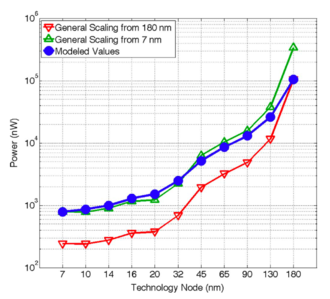

However, many advances in CMOS fabrication processes are, most of the time, driven by the performance requirements of digital circuits. As we can see in Figs. 1-3, scaling offers significant improvement in device area, speed, and power consumption.

Figure 1: Area improvement[1]. |

Figure 2: Delay improvement[1]. |

Figure 3: Power consumption[1]. |

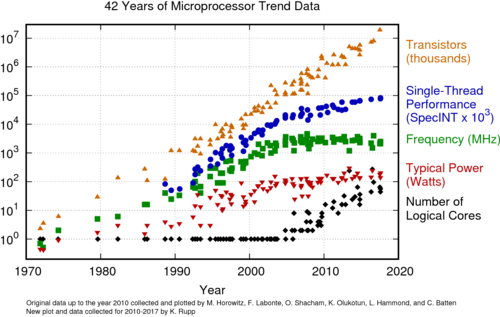

In many cases, this reduction in delay, which translates to increased clock frequencies, it not really realized, due to the increased heat dissipation requirements at high clock frequencies, since , where is the activity factor of a digital circuit, is the effective capacitance being driven, is the supply voltage, and is the clock frequency. This is evident in Fig. 4, where even though the transistor count increases due to scaling, the power limits the further increase in clock frequencies. Thus, in order to increase performance, designers use "More than Moore" techniques such as parallelism.

Figure 4: Scaling and processor performance[2]. |

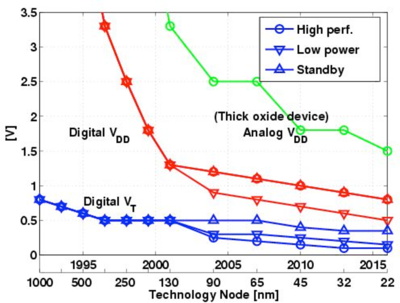

Figure 5: Supply and threshold voltage scaling[3]. |

One way to reduce the power consumption of digital circuits is to reduce the supply voltage, as seen in Fig. 5. In many ways, as we will see during the semester, reducing the supply voltage makes analog design harder by (1) reducing the signal-to-noise ratios, and (2) increasing the effect of variability as illustrated in Fig. 6. The task of the digital and analog designer, therefore, is to design circuits that operate reliably in the face of the various constraints imposed by the fabrication process.

Proceed to the next module: Scaling

References

- ↑ Jump up to: 1.0 1.1 1.2 Aaron Stillmaker, Bevan Baas, Scaling equations for the accurate prediction of CMOS device performance from 180nm to 7nm, Integration, Volume 58, 2017, Pages 74-81, ISSN 0167-9260, https://doi.org/10.1016/j.vlsi.2017.02.002.

- ↑ Karl Rupp, 42 Years of Microprocessor Trend Data, https://www.karlrupp.net/2018/02/42-years-of-microprocessor-trend-data/

- ↑ ITRS, The International Technology Roadmap for Semiconductors (2004 edition), 2004. Technical Report, http://public.itrs.net

- ↑ Rob A. Rutenbar (CMU)