Difference between revisions of "Integrated Capacitors"

| Line 34: | Line 34: | ||

|- | |- | ||

|} | |} | ||

| + | |||

| + | == PVT Variations == | ||

| + | Similar to integrated resistors, integrated capacitors are heavily dependent on the limitations and characteristics of the CMOS fabrication process. Thus, like resistors, also suffer from process variations and mismatch, as well as exhibit temperature and voltage dependencies, as shown in Table 1. | ||

| + | |||

| + | {| class = "wikitable" style="text-align: center;" | ||

| + | |+ Table 1: Illustrative Capacitance Characteristics | ||

| + | ! Type | ||

| + | ! <math>C\,\mathrm{[aF/\mu m^2]}</math> | ||

| + | ! <math>V_C\,\mathrm{[ppm/V]}</math> | ||

| + | ! <math>T_C\,\mathrm{[ppm/^\circ C]}</math> | ||

| + | |- | ||

| + | | polysilicon-polysilicon (option) | ||

| + | | 1000 | ||

| + | | 10 | ||

| + | | 25 | ||

| + | |- | ||

| + | | metal-metal | ||

| + | | 50 | ||

| + | | 20 | ||

| + | | 30 | ||

| + | |- | ||

| + | | metal-substrate | ||

| + | | 30 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | metal-polysilicon | ||

| + | | 50 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | polysilicon-substrate | ||

| + | | 120 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | |} | ||

| + | |||

== References == | == References == | ||

<references /> | <references /> | ||

Latest revision as of 06:42, 22 September 2020

Similar to resistors, in a CMOS process optimized for digital circuits, capacitances are treated as parasitic devices that degrade the performance of digital circuits, except in specialized cases such as memory circuits. However, in analog design, we often need capacitors with very well-controlled capacitance values.

Contents

Capacitor Geometries

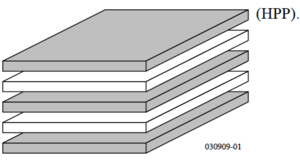

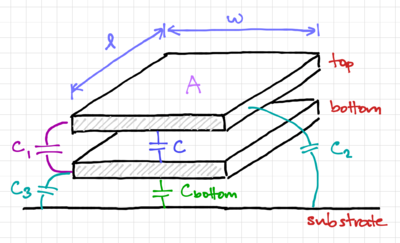

We can create parallel-plate capacitors using the routing layers, typically a metal layer, separated by the inter-layer dielectric (ILD), typically silicon dioxide. Thus, these structures are known as metal-oxide-metal (MOM) capacitors. The parallel-plate capacitance of the MOM structure shown in Fig. 1, is given by:

-

(1)

-

Where is the capacitance density, or capacitance per unit area, of a particular layer, is the permittivity of the dielectric or insulating material, is the thickness of the dielectric, and is the overlap area of the parallel-plate.

Parasitic Capacitances

In addition to the main parallel-plate capacitance, , we would get the following parasitic capacitances:

- A bottom plate parasitic capacitance, , between the bottom plate and the substrate.

- Perimeter-dependent fringing capacitances, due to the fringing electric fields between the:

- top plate and bottom plate, , resulting in an increase in the main capacitance predicted by the parallel-plate expression in Eq. 1,

- top plate and substrate, , adding a top plate parasitic capacitance, and

- bottom plate and substrate, , again adding to the capacitance predicted by our parallel-plate formula.

Note that it is much harder to model and predict the capacitance due to the non-uniform fringing electric fields. We can reduce the effects of the fringing fields by making the main capacitance much larger than the parasitic fringing capacitances by minimizing the perimeter of the parallel-plate structure.

Alternative Parallel-Plate Structures

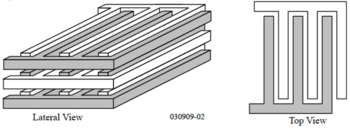

To support the increasing complexity of digital circuits, additional routing layers have been made available in advanced CMOS processes. This increase in metal layers opens up the possibility of using multiple layers, shown in Fig. 2, or even horizontal electric fields, in addition to vertical fields, as seen in Figs. 3 and 4, in creating very high-density, and well controlled, capacitor structures.

Figure 2: Stacked horizontal parallel-plates[1]. |

Figure 3: Vertical parallel-plates[1]. |

Figure 4: Combining vertical and horizontal parallel-plates[1]. |

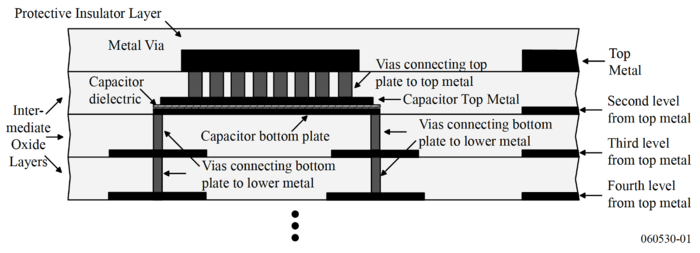

In instances where larger capacitance densities are required, CMOS processes may offer metal-insulator-metal or MIM capacitor options, where a special metal layer is added, separated by a thin insulator to the metal routing layer underneath, as shown in Fig. 5.

Figure 5: A MIM Capacitor[2]. |

PVT Variations

Similar to integrated resistors, integrated capacitors are heavily dependent on the limitations and characteristics of the CMOS fabrication process. Thus, like resistors, also suffer from process variations and mismatch, as well as exhibit temperature and voltage dependencies, as shown in Table 1.

| Type | |||

|---|---|---|---|

| polysilicon-polysilicon (option) | 1000 | 10 | 25 |

| metal-metal | 50 | 20 | 30 |

| metal-substrate | 30 | ||

| metal-polysilicon | 50 | ||

| polysilicon-substrate | 120 |

![{\displaystyle C\,\mathrm {[aF/\mu m^{2}]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/b4bd9575418ce20a1ea7ff8f7a2e53157d6943ce)

![{\displaystyle V_{C}\,\mathrm {[ppm/V]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/2999d120b9c9f1a9b2dffbdfb528de8b30f600a1)

![{\displaystyle T_{C}\,\mathrm {[ppm/^{\circ }C]} }](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/04b91e8231c6b3dfb9f275182a37fa14a115d0b4)