Difference between revisions of "CoE 197U MOS Differential Pairs"

(Created page with "The differential pair is one of the most commonly used circuit blocks in analog IC design. It enables amplifiers to have not just two, but specifically, differential inputs an...") |

(→Gain) |

||

| (27 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

The differential pair is one of the most commonly used circuit blocks in analog IC design. It enables amplifiers to have not just two, but specifically, differential inputs and act based only or mostly on the difference of the input signals. | The differential pair is one of the most commonly used circuit blocks in analog IC design. It enables amplifiers to have not just two, but specifically, differential inputs and act based only or mostly on the difference of the input signals. | ||

| − | The main references for this topic are chapters 3.5 and 4.3.5 of the Analysis and Design of Analog Integrated Circuits book. | + | The main references for this topic are chapters 3.5 and 4.3.5 of the Analysis and Design of Analog Integrated Circuits book<ref>Gray, Hurst, Lewis, Meyer, '''Analysis & Design of Analog Integrated Circuits''', Wiley 2001.</ref>. |

== Fully Differential Amplifier Signal and Gain Definitions == | == Fully Differential Amplifier Signal and Gain Definitions == | ||

| + | |||

| + | Before proceeding, the voltage signals to be dealt with need to be defined first to aid in the discussion. We will look at a general fully differential amplifier with a differential input and a differential output. The differential input/output voltages are the difference of input/output voltages. The common-mode input/output voltages are the average of the input/output voltages. Given how <math>v_1</math>, <math>v_2</math>, <math>v_d</math>, and <math>v_d</math> are related (Fig. 1), knowledge of any two can be used to infer the remaining two. | ||

| + | {| | ||

| + | | | ||

| + | [[File:Fully Differential Amplifier Voltage Definitions.png|thumb|450px|Fig. 1Fully Differential Amplifier Voltage Definitions]] | ||

| + | | | ||

| + | [[File:Fully Differential Amplifier Voltage Gain Definitions.png|thumb|350px|Fig. 2 Fully Differential Amplifier Voltage Gain Definitions]] | ||

| + | | | ||

| + | [[File:Cancellation of Common-mode Noise in Differential Signal.png|thumb|350px|Fig. 3 Cancellation of Common-mode Noise in Differential Signal]] | ||

| + | |} | ||

| + | |||

| + | The presence of differential and common-mode inputs and outputs require a clarification on how the gains are defined (Fig. 2). An ideal fully differential amplifier will have a very large <math>A_{dm}</math> and very low <math>A_{cm}</math>, as the arrows' thickness suggests. <math>A_{cm-dm}</math> and <math>A_{dm-cm}</math> are also ideally very low. <math>A_{cm-dm}</math> and <math>A_{dm-cm}</math> are both zero if the circuit is perfectly balanced, which requires that components are perfectly matched in terms of device properties and bias. | ||

| + | |||

| + | The advantage of having a differential input is the ability to reject signals that are common to both inputs such as noise that is coupled to both input signals. As can be seen in Fig. 3, the noise present on both inputs, <math>v_{1}</math> and <math>v_{2}</math>, does not appear at the differential signal <math>v_{d}</math>. If indeed the differential pair works only on this differential input signal, then the noise will not be amplified with the actual input information. The same property also allows the circuit to be less sensitive to the DC offset of the two signals. This makes differential amplifiers easy to cascade without the need for AC-coupling capacitors, which generally need to be large and are costly in IC implementations. However, care is still needed when dealing with large signal swings and/or small supply voltages. | ||

| + | |||

== DC and Large Signal Analysis == | == DC and Large Signal Analysis == | ||

| − | == Small Signal AC and Half Circuit Analysis == | + | |

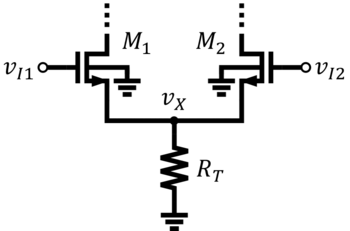

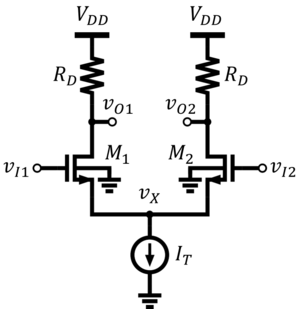

| + | The MOS differential pair or the source-coupled pair is shown in Figs. 4a and 4b. In source-coupled pairs, the source nodes are tied together. The current source is referred to as the tail current source. A simple but crude way of providing current to the differential pair is by using a tail resistor instead of a current source. | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: auto; border: none; width: 100%;" | ||

| + | |- style="vertical-align: bottom;" | ||

| + | | [[File:MOS differential pair biased with a tail current source.png|thumb|center|350px|Figure 4a: MOS differential pair with tail current source bias]] || [[File:MOS differential pair biased with a tail resistor.png|350px|thumb|center|Figure 4b: MOS differential pair with tail resistor bias]] || [[File:MOS differential pair drain currents as a function of differential input voltage.png|300px|thumb|center|Figure 5: MOS differential pair drain currents vs. differential input voltage]] | ||

| + | |} | ||

| + | |||

| + | Assume that the transistors are perfectly matched/identical. Assume also that anything connected above the drain terminals are perfectly balanced or symmetric. For the DC analysis, assume that <math>\lambda \rightarrow 0</math> for simplicity to highlight the basic operation of the circuit. | ||

| + | |||

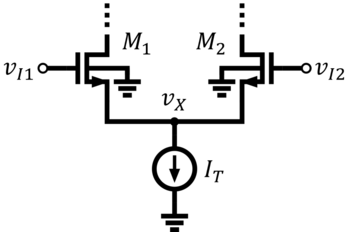

| + | Consider the differential pair with a tail current source (Fig. 4a). When there is no differential input, then the input voltages <math>V_{I1}</math> and <math>V_{I2}</math> must exactly be equal at some common-mode voltage <math>V_{IC}</math>. By virtue of symmetry, the transistors must have the same current, i.e. <math>I_{D1}=I_{D2}=I_{T}/2</math>. Such is the case without even taking note of what is the actual <math>V_{IC}</math>. If <math>V_{IC}</math> should change, <math>V_X</math> adjusts to maintain the Vgs that corresponds to <math>I_D=I_T/2</math>. Since <math>g_m</math> can be inferred from the transistor dimensions and the DC current, which are both constant, then <math>g_m</math> is maintained even if <math>V_{IC}</math> changes, again, under the assumption that <math>\lambda \rightarrow 0</math> or <math>r_o</math> is very large. | ||

| + | |||

| + | The large signal characteristics of the MOS differential pair analysis is started by setting up a KVL equation from <math>V_{i1}</math> to <math>V_{i2}</math> and relating it to currents <math>I_{d1}</math> and <math>I_{d2}</math>, under the restriction that <math>I_{d1}+I_{d2}=I_{T}</math>. The following equations are valid given that the two transistors are saturated. | ||

| + | ::Disregarding <math>\lambda</math>, <math>I_D=\frac{1}{2}\mu_{eff}C_{ox}\frac{W}{L}\left(V_{GS}-V_{TH}\right)^2=\frac{1}{2}k'\frac{W}{L}\left(V_{GS}-V_{TH}\right)^2</math> | ||

| + | ::For <math>|V_{id}|<V_{id,max}=\sqrt{\frac{2I_T}{k'\frac{W}{L}}}</math>: | ||

| + | {{NumBlk|::|<math>I_{d1}=\frac{I_{T}}{2}+\frac{k'}{4}\frac{W}{L}V_{id}\sqrt{\frac{4I_T}{k'\frac{W}{L}}-V_{id}^2}</math>|{{EquationRef|1}}}} | ||

| + | {{NumBlk|::|<math>I_{d2}=\frac{I_{T}}{2}-\frac{k'}{4}\frac{W}{L}V_{id}\sqrt{\frac{4I_T}{k'\frac{W}{L}}-V_{id}^2}</math>|{{EquationRef|2}}}} | ||

| + | |||

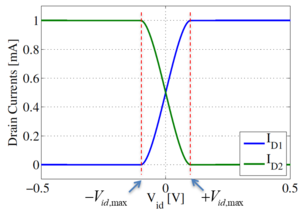

| + | When <math>|V_{id}|>V_{id,max}</math>, all of <math>I_T</math> will flow only through one transistor while the other transistor will be in cut-off. This is shown in Fig. 5. Thus, the tail current is effectively steered or distributed between M1 and M2 by <math>V_{id}</math>, regardless of the <math>V_{ic}</math> as long as the transistors are saturated and the current source is still operating as intended. | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: auto; border: none; width: 100%; vertical-align: bottom" | ||

| + | |- style="vertical-align: bottom;" | ||

| + | | | ||

| + | [[File:MOS differential pair with resistor load.png|thumb|300px|center|Figure 6: MOS differential pair with resistor load]] | ||

| + | || | ||

| + | [[File:Differential pair with resistor load Vod vs Vid.png|thumb|400px|center|Figure 7: Vod vs. Vid of differential amplifier with resistor load]] | ||

| + | |} | ||

| + | |||

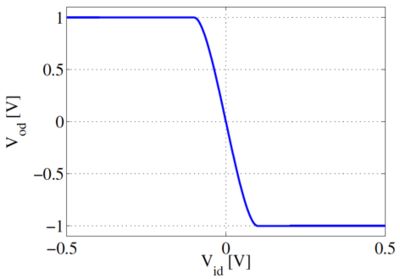

| + | Assuming that the load is a pair of equal and matched resistors such in Fig. 6, the output voltage is determined by KVL (Eq. 3) and the difference in drain currents (Eqs. 1 and 2). The resulting expression is Eq. 4. The plot of this function is the middle portion of Fig. 7. | ||

| + | |||

| + | {{NumBlk|::|<math>V_{od}=V_{o1}-V_{o2}=(V_{CC}-I_{d1}R_D)-(V_{CC}-I_{d2}R_D)</math>|{{EquationRef|3}}}} | ||

| + | ::For <math>|V_{id}|<V_{id,max}</math>: | ||

| + | {{NumBlk|::|<math>V_{od}=-R_D\frac{k'}{2}\frac{W}{L}V_{id}\sqrt{\frac{4I_T}{k'\frac{W}{L}}-V_{id}^2}</math>|{{EquationRef|4}}}} | ||

| + | |||

| + | Beyond <math>|V_{id,max}|</math> the currents rail, and therefore, the differential output voltage also rail. Fig. 7 also shows that the amplifier has an inverting gain. | ||

| + | |||

| + | <math>V_{id,max}</math> can also be rewritten as <math>\sqrt{2}\cdot \left(V_{GS}-V_{TH}\right)</math>. Thus, designing the differential pair with a larger <math>\left(V_{GS}-V_{TH}\right)</math> increases the differential input voltage range at which both transistors are saturated. However, it will be shown on later in this module that a larger ''overdrive voltage'' of the differential pair leads to poorer gain, CMRR, and sensitivity to mismatch. | ||

| + | ::<math>V_{id,max}=\sqrt{2}\cdot \left(V_{GS}-V_{TH}\right)</math> | ||

| + | |||

| + | == Small-Signal AC and Half Circuit Analysis == | ||

| + | Taking the limit as <math>V_{id}\rightarrow 0</math>, it can be shown that the <math>v_{od}(v_{id})</math> approaches a linear function, and the small-signal gain is <math>-g_mR_D </math> which must be very familiar. Note that this <math>g_m</math> is evaluated at the case where <math>V_{id}</math> is around 0, where <math>I_{D1}\approx I_{D2}\approx \frac{I_T}{2}</math>, and that the small-signal gain represents the slope of the <math>V_{od}</math> vs. <math>V_{id}</math> plot for very small <math>V_{id}</math>. The expression is not very accurate because Eqs. 4 and 5 assumes that <math>r_o</math> is very large. | ||

| + | |||

| + | ::<math>A_{dm}=\frac{v_{od}}{v_{id}}=\left.\frac{\partial V_{od}}{\partial V_{id}}\right|_{V_{id}\rightarrow 0}</math> | ||

| + | ::<math>A_{dm}\approx -R_D\frac{k'}{2}\frac{W}{L}\sqrt{\frac{4I_T}{k'\frac{W}{L}}}</math> | ||

| + | {{NumBlk|::|<math>A_{dm}\approx -R_D\sqrt{2k'\frac{W}{L}\left(\frac{I_T}{2}\right)} = -R_D\sqrt{2k'\frac{W}{L}I_{D1}} = -R_D\sqrt{2k'\frac{W}{L}I_{D2}} = -g_mR_D</math>|{{EquationRef|5}}}} | ||

| + | |||

| + | Eq. 5 shows that the small-signal differential gain is dependent only on <math>R_D</math>, the transistor dimensions, and the tail current. Changing the DC bias of the input voltage will not affect the gain, as long as the transistors are saturated and the tail current is fixed. | ||

| + | |||

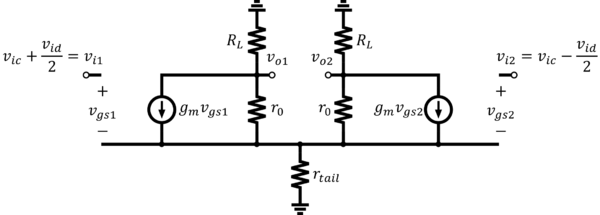

| + | Analyzing the circuit’s small-signal model will help determine the small-signal gains easier, without having to assume that <math>r_o\rightarrow \infty</math>. The full small-signal equivalent circuit is shown in Fig. 8. Here we are assuming that the tail current source is non-ideal and has some finite small-signal resistance <math>r_{tail}</math>. Note also, that transistors’ <math>r_o</math> are maintained. | ||

| + | |||

| + | [[File:Small signal equivalent circuit of the MOS differential amplifier with resistor load.png|thumb|600px|center|Figure 8: Small-signal equivalent circuit of the MOS differential amplifier with resistor load]] | ||

| + | |||

| + | The differential gain <math>A_{dm}</math> is analyzed with <math>v_{ic}=0</math>. If the circuit is perfectly balanced, it follows that <math>v_{oc}=0</math>. Due to symmetry, analyzing only half of the circuit should already give us enough information. With differential inputs only in play, one side/half can be considered “positive” while the other side/half can be considered “negative.” Thus, the middle point/s of the differential circuit must be at small-signal 0V. We can divide the circuit in half and place a virtual differential ground at each wire that is cut by the axis of symmetry. Note, however, that we must still maintain the voltage definitions with <math>v_{ic}=0</math> (i.e. <math>v_{i1}</math> remains <math>+\frac{v_{id}}{2}</math>, etc.) as in Fig. 9. | ||

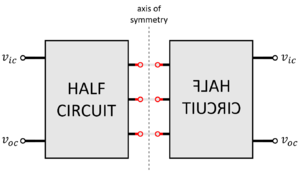

| + | |||

| + | {| style="margin-left: auto; margin-right: auto; border: none; width: 100%;" | ||

| + | |- | ||

| + | | [[File:Determining the differential half circuit.png|thumb|center|Figure 9: Determining the differential half circuit ]] || | ||

| + | [[File:Differential half circuit of the differential pair with resistor load.png|thumb|center|Figure 10: Differential half circuit of the differential pair with resistor load]] | ||

| + | |} | ||

| + | |||

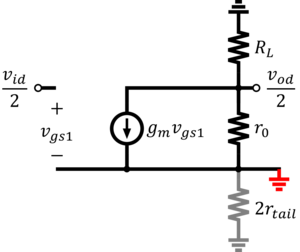

| + | Taking the left-side of Fig. 8 for the differential half circuit analysis, we end up with Fig. 10. Note that the voltages are still <math>+\frac{v_{id}}{2}</math> and <math>+\frac{v_{od}}{2}</math>. The tail resistance was also divided into two <math>2\cdot r_{tail}</math>’s to properly cut the circuit in half. The source is at (differential) ground, and thus, <math>r_{tail}</math> is effectively shorted. The remaining portion of the half circuit resembles that of a resistor-loaded common source, whose gain is <math>-g_m\left(r_o||R_D\right)</math>. However, the input is <math>\frac{v_{id}}{2}</math> while the output is <math>\frac{v_{od}}{2}</math>. Thus, this gain is given by: | ||

| + | |||

| + | ::<math>\frac{v_{od}/2}{v_{id}/2}=-g_m\left(r_o||R_L\right)</math> | ||

| + | {{NumBlk|::|<math>A_{dm}=\frac{v_{od}}{v_{id}}=-g_m\left(r_o||R_L\right)</math>|{{EquationRef|6}}}} | ||

| + | |||

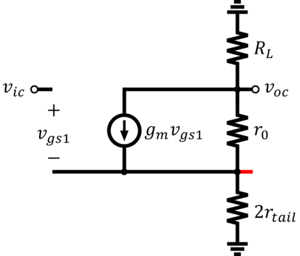

| + | For the common-mode case, <math>v_{id}</math> must be set to zero which consequently makes <math>v_{od}=0</math>. This time, since we are applying common or the same excitation on both sides of a balanced circuit then, there must be no current flowing either from left to right or from right to left since the two sides are at the same potential. Thus, portions that are cut in dividing the circuit into two are left open, instead of placing a ground, as shown in Fig. 11. The common-mode half circuit is shown in Fig. 12. This circuit follows the same structure as a common source amplifier with emitter degeneration, and with <math>R_C=R_L</math> and <math>R_E=2r_{tail}</math>. The gain of such a circuit is approximately <math>\frac{-g_mR_C}{1+g_mR_E}</math>. Thus, the common-mode gain is given by Eq. 7. Note that if the current source were ideal, then <math>r_{tail}\rightarrow \infty</math> and <math>A_{cm}\rightarrow 0</math>. | ||

| + | |||

| + | {{NumBlk|::|<math>A_{cm}=\frac{v_{oc}}{v_{ic}}\approx-\frac{g_mR_L}{1+g_m\cdot 2r_{tail}}</math>|{{EquationRef|7}}}} | ||

| + | |||

| + | {| style="margin-left: auto; margin-right: auto; border: none; width: 75%;" | ||

| + | |- | ||

| + | | [[File:Determining the common-mode half circuit.png|thumb|center|Figure 11: Determining the common-mode half circuit]] || | ||

| + | [[File:Common-mode half circuit of the differential pair with resistor load.png|thumb|center|Figure 12: Common-mode half circuit of the differential pair with resistor load]] | ||

| + | |} | ||

| + | |||

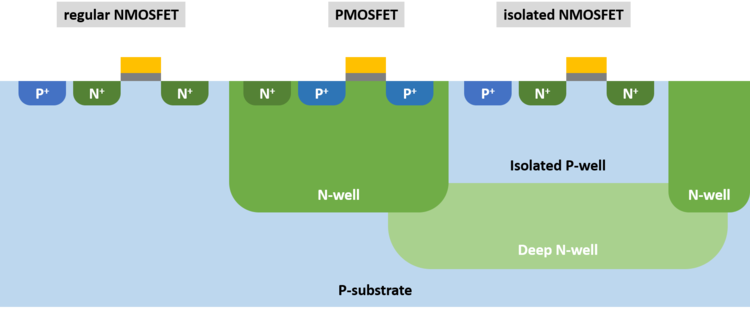

| + | Note that the previous expression is valid only when there is '''no''' body effect. However, this is not true for the circuit in Fig. 6 since the body is grounded while the source is not. In a standard CMOS technology with a p-type substrate, shorting the PMOS source to its body is easy since each PMOS has its own n-well. However, for NMOS, the body is also the substrate that is shared across the whole chip. It will only be possible to short the NMOS source to the body, without shorting the rest of the substrate, if the technology has a way to isolate and tap an NMOS’s p-type body from the rest of the chip. Such a feat is possible with a ''triple well'' technology (Fig. 13). | ||

| + | |||

| + | [[File:Transistors in a triple-well technology.png|thumb|750px|center|Figure 13: Transistors in a triple-well technology]] | ||

| + | |||

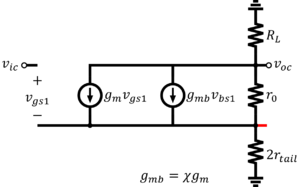

| + | If the body is not or cannot be tied to the source, then the body effect occurs, where changes in <math>v_{BS}</math> cause threshold voltage to change. Thus, when the source potential changes, the drain current changes not only because <math>v_{GS}</math> changes but also because the threshold voltage changes. The small-signal common-mode half circuit with the body effect is shown in Fig. 14. Analysis of this half circuit will lead to a common-mode gain expressed by Eq. 8. Note that the body transconductance is given by <math>g_{mb}=\chi g_m</math> | ||

| + | |||

| + | {{NumBlk|::|<math>A_{cm}=-G_{m,cm}\cdot R_{o,cm}\approx -\frac{g_m}{1+g_m\left(1+\chi\right)\cdot 2r_{tail}}\cdot R_L||\left(r_o+2r_{tail}+g_m\left(1+\chi\right)r_o\cdot 2r_{tail}\right)</math>|{{EquationRef|8}}}} | ||

| + | ::<math>A_{cm}\approx -\frac{g_mR_L}{1+g_m\left(1+\chi\right)\cdot 2r_{tail}}</math> | ||

| + | |||

| + | [[File:Common-mode half circuit of the resistor-loaded differential pair with body effect.png|thumb|center|Figure 14: Common-mode half circuit of the resistor-loaded differential pair with body effect]] | ||

| + | |||

| + | Note that there is no body effect in the differential circuit even if the source not shorted to the body since the bulk is grounded and the source is at the differential ground. Thus, the small-signal <math>v_{bs}</math> is 0. | ||

| + | |||

=== CMRR === | === CMRR === | ||

| + | |||

| + | {{NumBlk|::|<math>CMRR=\left|\frac{A_{dm}}{A_{cm}}\right|</math>|{{EquationRef|9}}}} | ||

| + | |||

| + | The common-mode rejection ratio or CMRR is given by Eq. 9. CMRR is a primary figure of merit for differential amplifiers. The higher the CMRR, the better. For the differential pair with body effect, the CMRR is approximately given by Eq. 10. The CMRR of the differential amplifier improves with increasing <math>r_{tail}</math> and is independent of the load resistance. The equation also shows that the body effect helps improve CMRR since χ is a positive quantity typically around 0.1 to 0.3. Although the body-effect improves CMRR by reducing Acm, it must be noted that the body effect still influences the threshold voltage and can impact the allowable DC voltage levels and signal swing. | ||

| + | |||

| + | {{NumBlk|::|<math>CMRR \approx 1+g_m\left(1+\chi\right)\cdot 2r_{tail}</math>|{{EquationRef|10}}}} | ||

| + | |||

| + | Eq. 10 can be expressed in terms of the transistor currents and overdrive voltage. Assuming that the tail current source is some NMOS transistor biased at saturation, then the tail resistance must be some <math>r_{o}</math>, and the expressions below can be obtained. The equations show that to improve CMRR, the length of the tail current source transistor must be increased (to decrease <math>\lambda_T</math>) while the overdrive of the differential pair must be decreased (larger width-length ratio for the same current). | ||

| + | |||

| + | ::<math>CMRR\approx 1+\frac{2I_{D1}}{V_{OV1}}\left(1+\chi\right)\cdot 2\left(\frac{1}{\lambda_T I_T}\right)</math> | ||

| + | ::<math>CMRR\approx 1+\frac{2\left(1+\chi\right)}{V_{OV1}\cdot \lambda_{T}}</math> | ||

| + | |||

== Differential Pair with Active Load == | == Differential Pair with Active Load == | ||

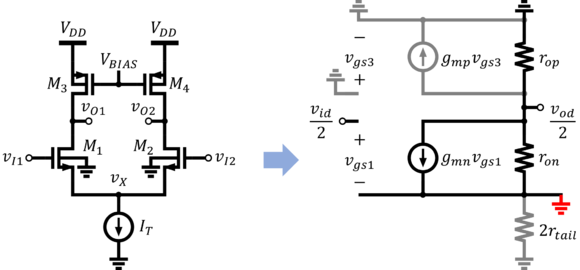

| + | Larger gains can be achieved when using active loads. Fig. 15 shows an active-loaded differential pair. The two load transistors act like current sources. M3 and M4 must be biased such that <math>I_{D3}=I_{D4}=\frac{I_T}{2}</math> at DC. | ||

| + | |||

| + | At AC, the gates of M3 and M4 are grounded since <math>V_{BIAS}</math> is some constant voltage bias or reference. Aside from that, the gates of M3 and M4 are at differential ground. Thus, at AC, <math>v_{gs3,4}=0</math>, M3 and M4 simply present a resistance <math>r_{op}</math>, and the differential gain must be | ||

| + | {{NumBlk|::|<math>A_{dm}=-g_{mn}\left(r_{on}\parallel r_{op}\right)</math>|{{EquationRef|11}}}} | ||

| + | |||

| + | [[File:Differential pair with active load and the equivalent circuit for small-signal analysis.png|thumb|580px|center|Figure 15: Differential pair with active load and the equivalent circuit for small-signal analysis]] | ||

| + | |||

| + | Although the gain of this circuit is larger compared to the resistor-loaded case, maintaining the correct DC operation is harder. Note that the output DC voltage is not well-defined unlike in the resistor-loaded case where <math>v_{o1,2}</math> can be easily found to be <math>V_{DD}-I_{D1,2}R_L</math>. Even a minor mismatch between <math>I_{D3}</math>, <math>I_{D4}</math>, and <math>\frac{I_T}{2}</math> will cause the output nodes to rail up or down, putting the load transistors or the differential pair in the linear region, respectively. Thus, some form of '''common-mode feedback or CMFB''' is necessary to ensure that the active-loaded differential pair will have a stable DC output level and to ensure that transistors are saturated. CMFB is discussed in Chapter 12.4 of the book (optional, for further reading). | ||

| + | |||

== Differential to Single-Ended Output Conversion == | == Differential to Single-Ended Output Conversion == | ||

| + | |||

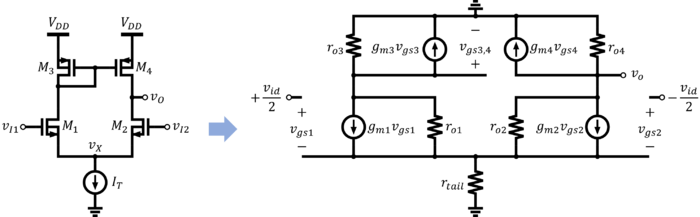

| + | A lot of applications require a single-ended output. However, the differential pair’s output is differential by default. Taking the output from one side will cut the transconductance in half, and thus, the gain in half. This is not an ideal scenario since we are paying with current and power to increase <math>g_m</math> but benefitting only from half of it. A better way to convert from a differential to a single-ended output is using a current mirror load (Fig. 16). | ||

| + | |||

| + | [[File:Differential pair with current mirror load and the equivalent circuit for small-signal analysis.png|700px|thumb|center|Figure 16: Differential pair with current mirror load and the equivalent circuit for small-signal analysis]] | ||

| + | |||

=== DC Analysis === | === DC Analysis === | ||

| − | === Small Signal AC Analysis === | + | The mirroring action happens in both DC and AC. At DC, the current <math>I_{D3}</math> will be mirrored to <math>I_{D4}</math>. If the transistors are perfectly matched and <math>V_{ID}=0</math>, then <math>I_{D1}=I_{D2}=I_{D3}=I_{D4}</math>. Note that this circuit does not require a separate biasing circuit since the diode-connected M3 automatically generates the necessary gate voltage. Also, if the transistors are perfectly matched and if indeed the currents through M3 and M4 are the same, then, <math>V_O</math> must be at the same potential as the drain of M3. |

| + | |||

| + | ::<math>V_{GS3}=V_{GS4}</math> | ||

| + | ::<math>I_{D3}=I_{D4}</math> | ||

| + | ::<math>k\left(\left|V_{GS3,4}\right|-\left|V_{TH,p}\right|\right)\left(1+\lambda_p\left|V_{DS3}\right|\right)=k\left(\left|V_{GS3,4}\right|-\left|V_{TH,p}\right|\right)\left(1+\lambda_p\left|V_{DS4}\right|\right)</math> | ||

| + | ::<math>\left(1+\lambda_p\left|V_{DS3}\right|\right)=\left(1+\lambda_p\left|V_{DS4}\right|\right)</math> | ||

| + | ::<math>V_{DS3}=V_{DS4}</math> | ||

| + | ::<math>V_O=V_{G3}=V_{G4}=V_{D3}</math> | ||

| + | |||

| + | === Small-Signal AC Analysis === | ||

| + | |||

| + | The small-signal model of the current mirror-loaded differential pair is also shown in Fig. 16. Because the load is not anymore balanced (M3 is diode-connected while M4 is not), then, half circuit analysis cannot be used. The tail current source is not anymore grounded, as there is no true differential ground in this circuit. The gain can be determined from the <math>G_m</math> and <math>R_{out}</math> of the circuit and using <math>A_V=-G_m R_{out}</math>. | ||

| + | |||

==== Transconductance ==== | ==== Transconductance ==== | ||

| + | |||

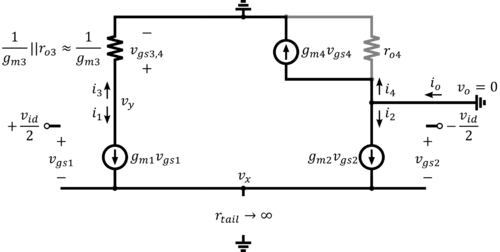

| + | For <math>G_m</math>, the output is grounded and the output current <math>i_o</math>, as stimulated from <math>v_{id}</math>, is measured (Fig. 17). Note that simplifying assumptions are used to come up with easy-to-interpret results. First, the tail current source is assumed to be ideal (i.e. <math>r_{tail}\rightarrow \infty</math>). Also, <math>r_{o1}</math> and <math>r_{o2}</math> are assumed to be very large, that they will not have a significant effect to the overall <math>G_m</math>. | ||

| + | |||

| + | [[File:Simplified small-signal circuit in determining Gm for the differential pair with current mirror load.png|500px|thumb|center|Figure 17: Simplified small-signal circuit in determining Gm for the differential pair with current mirror load]] | ||

| + | |||

| + | The diode-connected M3 can be modeled as a resistor with a value <math>\frac{1}{g_{m3}}</math> if <math>g_{m3}r_{o3}\gg1</math>. Note also that <math>r_{o4}</math> is shorted to ground at both sides and will not contribute any current to <math>i_o</math>. The current <math>i_4</math> can then be related to <math>i_3</math> as follows. Thus, in this case, the load will mirror the AC current perfectly if <math>g_{m3}r_{o3}\gg1</math>, the transistors are perfectly matched, and <math>I_{D3}=I_{D4}</math> which leads to <math>g_{m3}=g_{m4}</math>. | ||

| + | ::<math>i_4=g_{m4}v_{gs4}\approx g_{m4}\left(i_3\times\frac{1}{g_{m3}}\right)=i_3\frac{g_{m4}}{g_{m3}}</math> | ||

| + | ::<math>i_4\approx i_3</math> | ||

| + | |||

| + | Assume that <math>r_{tail}</math> is finite and that some current <math>i_{tail}</math> flows down from to ground. The equations below show that if the differential pair <math>r_o</math>'s are very large, then the voltage <math>v_x</math> is at 0V at small-signal. If the differential pair has equal currents at DC, then <math>g_{m1}=g_{m2}=g_{mn}</math> and <math>g_{m1}-g_{m2}=0</math>. Interestingly, the <math>r_{o1},r_{o2}\rightarrow \infty</math> assumption led to a conclusion that a differential ground approximately exists at the coupled source node. Note however that <math>r_{o1},r_{o2}\rightarrow \infty</math> cannot be assumed when analyzing the circuit's output resistance because <math>R_o</math> is expected to depend heavily on the transistors' <math>r_o</math>. | ||

| + | ::<math>i_1+i_2=i_{tail}</math> | ||

| + | ::<math>g_{m1}v_{gs1}+g_{m2}v_{gs2}\approx i_{tail}</math> disregarding <math>r_o</math>'s | ||

| + | ::<math>g_{m1}\left(+\frac{1}{2}v_{id}-v_x\right)+g_{m2}\left(-\frac{1}{2}v_{id}-v_x\right)\approx \frac{v_x}{r_{tail}}</math> | ||

| + | ::<math>g_{mn}\left(+\frac{1}{2}v_{id}-\frac{1}{2}v_{id}\right)\approx v_x\cdot\left(-g_{m1}-g_{m2}+\frac{1}{r_{tail}}\right)</math> | ||

| + | ::<math>0\approx v_x\cdot\left(-g_{m1}-g_{m2}+\frac{1}{r_{tail}}\right)</math> | ||

| + | ::<math>v_x\approx 0</math> | ||

| + | There is another reason why a differential ground approximately exists at the coupled source node in the circuit in Fig. 17, even with finite <math>r_{o1},r_{o2}</math>. | ||

| + | Note that the drain of M2 is shorted to ground while the drain of M1 is connected to a relatively small resistance, <math>\frac{1}{g_{m3}}</math>. If the resistance presented by M3 is small enough, then the drain of M1 is approximately at ground potential as well. Thus, the circuit operates in a nearly balanced behavior, and a differential ground appears at <math>v_x</math>. However, this observation is true only for the circuit in Fig. 17. The nearly balanced behavior does not occur anymore when analyzing the circuit's output resistance or voltage gain because in these cases, the output node is not anymore grounded. | ||

| + | |||

| + | Combining the fact that <math>v_x\approx 0</math> and that <math>r_{tail}</math> is normally very large, then <math>i_{tail}</math> must be very small and the tail resistance can be effectively treated as open circuit. This also means that | ||

| + | ::<math>i_2\approx-i_1</math>. | ||

| + | |||

| + | Since <math>v_x\approx 0</math>, then <math>v_{gs1}=v_{g1}-v_{s1}=+\frac{1}{2}v_{id}-v_x\approx+\frac{1}{2}v_{id}</math>. It can be shown in a similar fashion that <math>v_{gs2}\approx-\frac{1}{2}v_{id}</math>. | ||

| + | ::<math>v_{gs1}\approx +\frac{1}{2}v_{id}</math> | ||

| + | ::<math>v_{gs2}\approx -\frac{1}{2}v_{id}</math> | ||

| + | |||

| + | The currents <math>i_1</math>, <math>i_2</math>, and <math>i_3</math> can therefore be related as follows, where <math>g_{mn}</math> is used to denote <math>g_{m1}</math> and <math>g_{m2}</math>. | ||

| + | ::<math>i_3\approx i_2\approx -i_1=-g_{mn}v_{gs1}\approx-g_{mn}\frac{1}{2}v_{id}</math> | ||

| + | |||

| + | The output current <math>i_o</math> can finally be related to <math>v_{id}</math> by: | ||

| + | ::<math>i_o=i_4+i_2\approx i_3+i_2\approx 2i_3\approx-2g_{mn}\frac{1}{2}v_{id}</math> | ||

| + | ::<math>i_o\approx-g_{mn}v_{id}</math> | ||

| + | {{NumBlk|::|<math>G_m=\frac{i_o}{v_{id}}\approx-g_{mn}</math>|{{EquationRef|12}}}} | ||

| + | |||

==== Output Resistance ==== | ==== Output Resistance ==== | ||

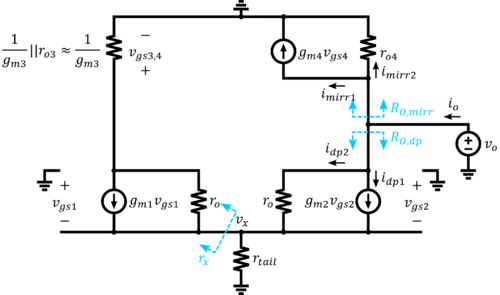

| + | For the output resistance analysis, the transistor <math>r_o</math>’s are retained as shown in Fig. 18. A test voltage is connected at the output and the drawn output current is measured while the input is grounded. <math>g_{m3}r_{o3}\gg1</math> is still assumed such that M3 is still modeled as some <math>\frac{1}{g_{m3}}</math> resistor. The output current branches into 4 components: <math>i_{mirr1}</math>, <math>i_{mirr2}</math>, <math>i_{dp1}</math>, and <math>i_{dp2}</math>. The output resistance can be considered to have two components such that | ||

| + | ::<math>R_o=R_{o,mirr}\parallel R_{o,dp}</math> | ||

| + | ::where <math>R_{o,mirr}=\frac{v_o}{i_{mirr1}+i_{mirr2}}</math> and <math>R_{o,dp}=\frac{v_o}{i_{dp1}+i_{dp2}}</math> | ||

| + | |||

| + | [[File:Simplified small-signal circuit in determining Ro for the differential pair with current mirror load.png|500px|thumb|center|Figure 18: Simplified small-signal circuit in determining Ro for the differential pair with current mirror load]] | ||

| + | |||

| + | The easiest to determine is <math>i_{mirr2}</math> which is just the current across the resistance <math>r_{o4}</math>. | ||

| + | ::<math>i_{mirr2}=\frac{v_o}{r_{o4}}</math> | ||

| + | |||

| + | The resistance presented by M1 and M3, as seen from the source of M2, can be lumped as some <math>r_x</math>. This <math>r_x</math> is in parallel with <math>r_{tail}</math>. The resistance <math>R_{o,dp}</math> can then be taken by analyzing M2 as an emitter degenerated transistor with an emitter resistance of <math>r_x\parallel r_{tail}</math>. An emitter degenerated transistor has the output resistance <math>R_{o,emitter\ degenerated}=r_o+R_E+g_mr_oR_E</math>. Thus, | ||

| + | ::<math>R_{o,dp}=r_{o2}+\left(r_x\parallel r_{tail}\right)+g_{m2}r_{o2}\left(r_x\parallel r_{tail}\right)</math> | ||

| + | |||

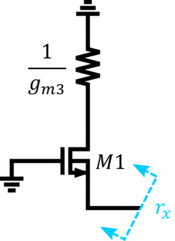

| + | [[File:Equivalent circuit in analyzing the resistance presented by M1 and M3.png|175px|thumb|center|Figure 19: Equivalent circuit in analyzing the resistance presented by M1 and M3]] | ||

| + | |||

| + | The resistance <math>r_x</math> (composed of M1 and M3) is obtained by analyzing the circuit in Fig. 19. The circuit can be seen as a source follower with some drain resistance. Refering to the original circuit of concern <math>R_D</math> is <math>\frac{1}{g_{m3}}</math> The complete expression is shown below although <math>r_x</math> is approximately <math>\frac{1}{g_{m1}}</math> , if <math>r_{o1}\gg \frac{1}{g_{m1}},\frac{1}{g_{m3}}</math>. | ||

| + | ::<math>r_x=\frac{r_{o1}+R_D}{1+g_{m1}r_{o1}}\rightarrow\frac{r_{o1}+\frac{1}{g_{m3}}}{1+g_{m1}r_{o1}}</math> | ||

| + | ::<math>r_x\approx \frac{1}{g_{m1}}</math> | ||

| + | |||

| + | An <math>r_x</math> of <math>\frac{1}{g_{m1}}</math> is normally very small compared to <math>r_{tail}</math>. Thus, <math>\left(r_x \parallel r_{tail} \right)\approx \frac{1}{g_{m1}}</math>, and the resistance presented by the differential pair is given below. Similarly, it is assumed that <math>r_{o2}\gg \frac{1}{g_{m1}}</math>. | ||

| + | ::<math>R_{o,dp}\approx r_{o2}+\frac{1}{g_{m1}}+g_{m2}r_{o2}\frac{1}{g_{m1}}\approx r_{o2}+g_{m2}r_{o2}\frac{1}{g_{m1}}=r_{o2}+r_{o2}</math> | ||

| + | ::<math>R_{o,dp}\approx 2r_{on}</math> | ||

| + | |||

| + | Since <math>r_x\approx \frac{1}{g_{m1}}\ll r_{tail}</math>, by current division, most of the current <math>\left(i_{dp1}+i_{dp2}\right)</math> will flow through <math>r_x</math>. Thus, the current through the resistance <math>\frac{1}{g_{m3}}</math> is almost the whole of <math>\left(i_{dp1}+i_{dp2}\right)</math> and will be mirrored through M4. | ||

| + | ::<math>i_{mirr1}=g_{m4}v_{gs4}\approx g_{m4}\left(\left(i_{dp1}+i_{dp2}\right)\frac{1}{g_m3}\right)</math> | ||

| + | ::<math>i_{mirr1}\approx i_{dp1}+i_{dp2}\approx \frac{v_o}{R_{o,dp}}</math> | ||

| + | |||

| + | The output resistance of the current mirror, from the component currents <math>i_{mirr1}</math> and <math>i_{mirr2}</math> is | ||

| + | ::<math>R_{o,mirr}=R_{o,mirr1}\parallel R_{o,mirr2}\approx R_{o,dp}\parallel r_{o4}</math> | ||

| + | |||

| + | Finally, the overall output resistance is the parallel combination of <math>R_{o,mirr}</math> and <math>R_{o,dp}</math>. | ||

| + | ::<math>R_o=R_{o,mirr}\parallel R_{o,dp}\approx \left(R_{o,dp}\parallel r_{o4}\right)\parallel R_{o,dp}</math> | ||

| + | ::<math>R_o\approx \frac{R_{o,dp}}{2}\parallel r_{op}\approx \frac{2r_{on}}{2}\parallel r_{op}</math> | ||

| + | {{NumBlk|::|<math>R_o\approx r_{on}\parallel r_{op}</math>|{{EquationRef|13}}}} | ||

| + | |||

| + | Following the discussion presented and assumptions used, the differential pair presents a resistance of <math>2r_{on}</math> (and not simply <math>r_{on}</math>) at the output terminal, while the current mirror presents a resistance of <math>2r_{on}\parallel r_{op}</math> (and not simply <math>r_{op}</math>). | ||

| + | |||

| + | In DC biased current mirrors, the output resistance will simply be the <math>r_o</math> of the output transistor. However, in this circuit, some AC current is being mirrored as well, so the output resistance is more complicated. | ||

| + | |||

==== Gain ==== | ==== Gain ==== | ||

| + | The gain of the current mirror-loaded differential pair with the assumptions discussed is given below. The gain is non-inverting since the output is taken on the side of the negative input terminal. | ||

| + | ::<math>A_v=\frac{v_o}{v_{id}}=-G_mR_o\approx -\left(-g_{mn}\right)\left(r_{on}\parallel r_{op}\right)</math> | ||

| + | {{NumBlk|::|<math>A_v\approx g_{mn}\left(r_{on}\parallel r_{op}\right)</math>|{{EquationRef|14}}}} | ||

| + | |||

| + | Although the gain expression turns out to be very simple, it is important to understand the analysis and assumptions done along the way. This should provide some background on what happens or what changes when some of the assumptions cannot be done anymore. The concepts discussed should also help when analyzing the circuit from a different perspective (e.g. analyzing with noise or parasitics) or analyzing a similar circuit (e.g. with cascoded differential pairs and/or cascoded current mirror loads). | ||

| + | |||

| + | == References == | ||

| + | <references /> | ||

Latest revision as of 11:28, 17 April 2021

The differential pair is one of the most commonly used circuit blocks in analog IC design. It enables amplifiers to have not just two, but specifically, differential inputs and act based only or mostly on the difference of the input signals.

The main references for this topic are chapters 3.5 and 4.3.5 of the Analysis and Design of Analog Integrated Circuits book[1].

Contents

Fully Differential Amplifier Signal and Gain Definitions

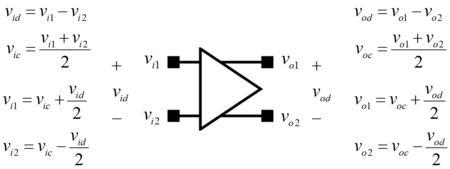

Before proceeding, the voltage signals to be dealt with need to be defined first to aid in the discussion. We will look at a general fully differential amplifier with a differential input and a differential output. The differential input/output voltages are the difference of input/output voltages. The common-mode input/output voltages are the average of the input/output voltages. Given how , , , and are related (Fig. 1), knowledge of any two can be used to infer the remaining two.

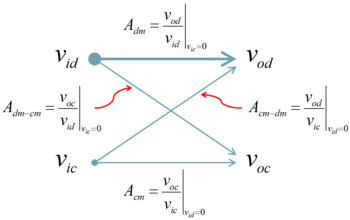

The presence of differential and common-mode inputs and outputs require a clarification on how the gains are defined (Fig. 2). An ideal fully differential amplifier will have a very large and very low , as the arrows' thickness suggests. and are also ideally very low. and are both zero if the circuit is perfectly balanced, which requires that components are perfectly matched in terms of device properties and bias.

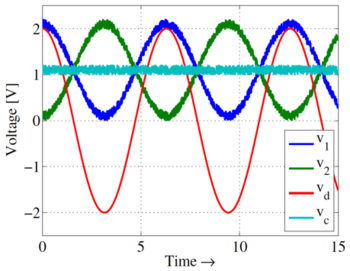

The advantage of having a differential input is the ability to reject signals that are common to both inputs such as noise that is coupled to both input signals. As can be seen in Fig. 3, the noise present on both inputs, and , does not appear at the differential signal . If indeed the differential pair works only on this differential input signal, then the noise will not be amplified with the actual input information. The same property also allows the circuit to be less sensitive to the DC offset of the two signals. This makes differential amplifiers easy to cascade without the need for AC-coupling capacitors, which generally need to be large and are costly in IC implementations. However, care is still needed when dealing with large signal swings and/or small supply voltages.

DC and Large Signal Analysis

The MOS differential pair or the source-coupled pair is shown in Figs. 4a and 4b. In source-coupled pairs, the source nodes are tied together. The current source is referred to as the tail current source. A simple but crude way of providing current to the differential pair is by using a tail resistor instead of a current source.

Assume that the transistors are perfectly matched/identical. Assume also that anything connected above the drain terminals are perfectly balanced or symmetric. For the DC analysis, assume that for simplicity to highlight the basic operation of the circuit.

Consider the differential pair with a tail current source (Fig. 4a). When there is no differential input, then the input voltages and must exactly be equal at some common-mode voltage . By virtue of symmetry, the transistors must have the same current, i.e. . Such is the case without even taking note of what is the actual . If should change, adjusts to maintain the Vgs that corresponds to . Since can be inferred from the transistor dimensions and the DC current, which are both constant, then is maintained even if changes, again, under the assumption that or is very large.

The large signal characteristics of the MOS differential pair analysis is started by setting up a KVL equation from to and relating it to currents and , under the restriction that . The following equations are valid given that the two transistors are saturated.

- Disregarding ,

- For :

-

(1)

-

-

(2)

-

When , all of will flow only through one transistor while the other transistor will be in cut-off. This is shown in Fig. 5. Thus, the tail current is effectively steered or distributed between M1 and M2 by , regardless of the as long as the transistors are saturated and the current source is still operating as intended.

Assuming that the load is a pair of equal and matched resistors such in Fig. 6, the output voltage is determined by KVL (Eq. 3) and the difference in drain currents (Eqs. 1 and 2). The resulting expression is Eq. 4. The plot of this function is the middle portion of Fig. 7.

-

(3)

-

- For :

-

(4)

-

Beyond the currents rail, and therefore, the differential output voltage also rail. Fig. 7 also shows that the amplifier has an inverting gain.

can also be rewritten as . Thus, designing the differential pair with a larger increases the differential input voltage range at which both transistors are saturated. However, it will be shown on later in this module that a larger overdrive voltage of the differential pair leads to poorer gain, CMRR, and sensitivity to mismatch.

Small-Signal AC and Half Circuit Analysis

Taking the limit as , it can be shown that the approaches a linear function, and the small-signal gain is which must be very familiar. Note that this is evaluated at the case where is around 0, where , and that the small-signal gain represents the slope of the vs. plot for very small . The expression is not very accurate because Eqs. 4 and 5 assumes that is very large.

-

(5)

-

Eq. 5 shows that the small-signal differential gain is dependent only on , the transistor dimensions, and the tail current. Changing the DC bias of the input voltage will not affect the gain, as long as the transistors are saturated and the tail current is fixed.

Analyzing the circuit’s small-signal model will help determine the small-signal gains easier, without having to assume that . The full small-signal equivalent circuit is shown in Fig. 8. Here we are assuming that the tail current source is non-ideal and has some finite small-signal resistance . Note also, that transistors’ are maintained.

The differential gain is analyzed with . If the circuit is perfectly balanced, it follows that . Due to symmetry, analyzing only half of the circuit should already give us enough information. With differential inputs only in play, one side/half can be considered “positive” while the other side/half can be considered “negative.” Thus, the middle point/s of the differential circuit must be at small-signal 0V. We can divide the circuit in half and place a virtual differential ground at each wire that is cut by the axis of symmetry. Note, however, that we must still maintain the voltage definitions with (i.e. remains , etc.) as in Fig. 9.

Taking the left-side of Fig. 8 for the differential half circuit analysis, we end up with Fig. 10. Note that the voltages are still and . The tail resistance was also divided into two ’s to properly cut the circuit in half. The source is at (differential) ground, and thus, is effectively shorted. The remaining portion of the half circuit resembles that of a resistor-loaded common source, whose gain is . However, the input is while the output is . Thus, this gain is given by:

-

(6)

-

For the common-mode case, must be set to zero which consequently makes . This time, since we are applying common or the same excitation on both sides of a balanced circuit then, there must be no current flowing either from left to right or from right to left since the two sides are at the same potential. Thus, portions that are cut in dividing the circuit into two are left open, instead of placing a ground, as shown in Fig. 11. The common-mode half circuit is shown in Fig. 12. This circuit follows the same structure as a common source amplifier with emitter degeneration, and with and . The gain of such a circuit is approximately . Thus, the common-mode gain is given by Eq. 7. Note that if the current source were ideal, then and .

-

(7)

-

Note that the previous expression is valid only when there is no body effect. However, this is not true for the circuit in Fig. 6 since the body is grounded while the source is not. In a standard CMOS technology with a p-type substrate, shorting the PMOS source to its body is easy since each PMOS has its own n-well. However, for NMOS, the body is also the substrate that is shared across the whole chip. It will only be possible to short the NMOS source to the body, without shorting the rest of the substrate, if the technology has a way to isolate and tap an NMOS’s p-type body from the rest of the chip. Such a feat is possible with a triple well technology (Fig. 13).

If the body is not or cannot be tied to the source, then the body effect occurs, where changes in cause threshold voltage to change. Thus, when the source potential changes, the drain current changes not only because changes but also because the threshold voltage changes. The small-signal common-mode half circuit with the body effect is shown in Fig. 14. Analysis of this half circuit will lead to a common-mode gain expressed by Eq. 8. Note that the body transconductance is given by

-

(8)

-

Note that there is no body effect in the differential circuit even if the source not shorted to the body since the bulk is grounded and the source is at the differential ground. Thus, the small-signal is 0.

CMRR

-

(9)

-

The common-mode rejection ratio or CMRR is given by Eq. 9. CMRR is a primary figure of merit for differential amplifiers. The higher the CMRR, the better. For the differential pair with body effect, the CMRR is approximately given by Eq. 10. The CMRR of the differential amplifier improves with increasing and is independent of the load resistance. The equation also shows that the body effect helps improve CMRR since χ is a positive quantity typically around 0.1 to 0.3. Although the body-effect improves CMRR by reducing Acm, it must be noted that the body effect still influences the threshold voltage and can impact the allowable DC voltage levels and signal swing.

-

(10)

-

Eq. 10 can be expressed in terms of the transistor currents and overdrive voltage. Assuming that the tail current source is some NMOS transistor biased at saturation, then the tail resistance must be some , and the expressions below can be obtained. The equations show that to improve CMRR, the length of the tail current source transistor must be increased (to decrease ) while the overdrive of the differential pair must be decreased (larger width-length ratio for the same current).

Differential Pair with Active Load

Larger gains can be achieved when using active loads. Fig. 15 shows an active-loaded differential pair. The two load transistors act like current sources. M3 and M4 must be biased such that at DC.

At AC, the gates of M3 and M4 are grounded since is some constant voltage bias or reference. Aside from that, the gates of M3 and M4 are at differential ground. Thus, at AC, , M3 and M4 simply present a resistance , and the differential gain must be

-

(11)

-

Although the gain of this circuit is larger compared to the resistor-loaded case, maintaining the correct DC operation is harder. Note that the output DC voltage is not well-defined unlike in the resistor-loaded case where can be easily found to be . Even a minor mismatch between , , and will cause the output nodes to rail up or down, putting the load transistors or the differential pair in the linear region, respectively. Thus, some form of common-mode feedback or CMFB is necessary to ensure that the active-loaded differential pair will have a stable DC output level and to ensure that transistors are saturated. CMFB is discussed in Chapter 12.4 of the book (optional, for further reading).

Differential to Single-Ended Output Conversion

A lot of applications require a single-ended output. However, the differential pair’s output is differential by default. Taking the output from one side will cut the transconductance in half, and thus, the gain in half. This is not an ideal scenario since we are paying with current and power to increase but benefitting only from half of it. A better way to convert from a differential to a single-ended output is using a current mirror load (Fig. 16).

DC Analysis

The mirroring action happens in both DC and AC. At DC, the current will be mirrored to . If the transistors are perfectly matched and , then . Note that this circuit does not require a separate biasing circuit since the diode-connected M3 automatically generates the necessary gate voltage. Also, if the transistors are perfectly matched and if indeed the currents through M3 and M4 are the same, then, must be at the same potential as the drain of M3.

Small-Signal AC Analysis

The small-signal model of the current mirror-loaded differential pair is also shown in Fig. 16. Because the load is not anymore balanced (M3 is diode-connected while M4 is not), then, half circuit analysis cannot be used. The tail current source is not anymore grounded, as there is no true differential ground in this circuit. The gain can be determined from the and of the circuit and using .

Transconductance

For , the output is grounded and the output current , as stimulated from , is measured (Fig. 17). Note that simplifying assumptions are used to come up with easy-to-interpret results. First, the tail current source is assumed to be ideal (i.e. ). Also, and are assumed to be very large, that they will not have a significant effect to the overall .

The diode-connected M3 can be modeled as a resistor with a value if . Note also that is shorted to ground at both sides and will not contribute any current to . The current can then be related to as follows. Thus, in this case, the load will mirror the AC current perfectly if , the transistors are perfectly matched, and which leads to .

Assume that is finite and that some current flows down from to ground. The equations below show that if the differential pair 's are very large, then the voltage is at 0V at small-signal. If the differential pair has equal currents at DC, then and . Interestingly, the assumption led to a conclusion that a differential ground approximately exists at the coupled source node. Note however that cannot be assumed when analyzing the circuit's output resistance because is expected to depend heavily on the transistors' .

- disregarding 's

There is another reason why a differential ground approximately exists at the coupled source node in the circuit in Fig. 17, even with finite . Note that the drain of M2 is shorted to ground while the drain of M1 is connected to a relatively small resistance, . If the resistance presented by M3 is small enough, then the drain of M1 is approximately at ground potential as well. Thus, the circuit operates in a nearly balanced behavior, and a differential ground appears at . However, this observation is true only for the circuit in Fig. 17. The nearly balanced behavior does not occur anymore when analyzing the circuit's output resistance or voltage gain because in these cases, the output node is not anymore grounded.

Combining the fact that and that is normally very large, then must be very small and the tail resistance can be effectively treated as open circuit. This also means that

- .

Since , then . It can be shown in a similar fashion that .

The currents , , and can therefore be related as follows, where is used to denote and .

The output current can finally be related to by:

-

(12)

-

Output Resistance

For the output resistance analysis, the transistor ’s are retained as shown in Fig. 18. A test voltage is connected at the output and the drawn output current is measured while the input is grounded. is still assumed such that M3 is still modeled as some resistor. The output current branches into 4 components: , , , and . The output resistance can be considered to have two components such that

- where and

The easiest to determine is which is just the current across the resistance .

The resistance presented by M1 and M3, as seen from the source of M2, can be lumped as some . This is in parallel with . The resistance can then be taken by analyzing M2 as an emitter degenerated transistor with an emitter resistance of . An emitter degenerated transistor has the output resistance . Thus,

The resistance (composed of M1 and M3) is obtained by analyzing the circuit in Fig. 19. The circuit can be seen as a source follower with some drain resistance. Refering to the original circuit of concern is The complete expression is shown below although is approximately , if .

An of is normally very small compared to . Thus, , and the resistance presented by the differential pair is given below. Similarly, it is assumed that .

Since , by current division, most of the current will flow through . Thus, the current through the resistance is almost the whole of and will be mirrored through M4.

The output resistance of the current mirror, from the component currents and is

Finally, the overall output resistance is the parallel combination of and .

-

(13)

-

Following the discussion presented and assumptions used, the differential pair presents a resistance of (and not simply ) at the output terminal, while the current mirror presents a resistance of (and not simply ).

In DC biased current mirrors, the output resistance will simply be the of the output transistor. However, in this circuit, some AC current is being mirrored as well, so the output resistance is more complicated.

Gain

The gain of the current mirror-loaded differential pair with the assumptions discussed is given below. The gain is non-inverting since the output is taken on the side of the negative input terminal.

-

(14)

-

Although the gain expression turns out to be very simple, it is important to understand the analysis and assumptions done along the way. This should provide some background on what happens or what changes when some of the assumptions cannot be done anymore. The concepts discussed should also help when analyzing the circuit from a different perspective (e.g. analyzing with noise or parasitics) or analyzing a similar circuit (e.g. with cascoded differential pairs and/or cascoded current mirror loads).

References

- ↑ Gray, Hurst, Lewis, Meyer, Analysis & Design of Analog Integrated Circuits, Wiley 2001.