CoE 197U Interconnects

In this lecture, we will cover topics on wires and interconnects.

Use the provided slide deck to guide you through this discussion. The main reference for this lecture is Chapter 4 of the Digital IC book[1]

Interconnects

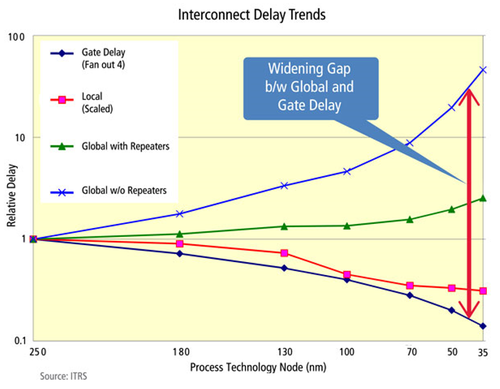

Wires are often neglected during design. They are simply used to connect signals from one point to another and assumed to have negligible effect on the performance of the system. Figure 1 shows the widening gap between wire delays and gate delays. As technology scales, dimensions and delays decrease. However, with the thinner interconnects, the wire resistance per unit length increases. As such, degradation in performance can be expected if they are not dealt with properly.

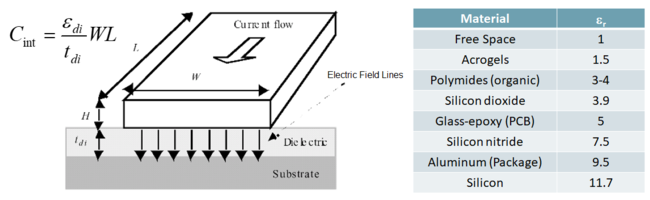

In terms of models, interconnects are represented as parasitics the degrade performance and reduce reliability of the system. Classes of parasistics are capacitive, resistive and inductive. For this course, we consider mostly capacitive and resistive. Any two parallel conductors with a dielectric in between can be treated as a capacitor. This is illustrated in Figure 2 and the corresponding equation shown. The parameter εdi if the permitivity of the dielectric. It is common to specify the relative permitivity, εr, of a material. That is, εdi = εrε0, where ε0 is the permitivity of free space and is equal to 8.854x10-12 F/m. Typical CMOS IC uses silicon dioxide as dielectric. The table below shows dielectric constants of other materials.

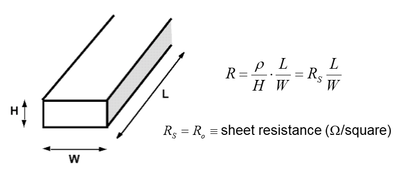

Any material will have some resistance. The equation is given in Fig. 3 , with the corresponding dimensions illustrated. Since the height (H) of the material is dictated by the manufacturing process, and the conductivity (rho) is determined by the material, then we can separate the length and width from the other parameters. The simplest model for interconnects is the lumped model, where total capacitance and total resistance of the conductor is computed and treated as a single RC network.

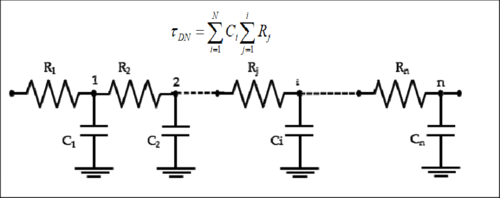

For long wires, the interconnect can be viewed as cascaded shorter wires, each having its R and C., as shown in Fig. 4. The path delay is computed using the given equation. For a sample problem and solution, you may watch the video: https://www.youtube.com/watch?v=1c_AgRmXQBw.

References

- ↑ J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, 2nd ed., 2002