Difference between revisions of "Lab 4: Flip-flop Flavors"

| Line 58: | Line 58: | ||

# Download the '''Lab 4 template''' in UVLe. | # Download the '''Lab 4 template''' in UVLe. | ||

| − | # Inside the ''dffButJK'' block, implement a D flip-flop with a JK flip-flop. | + | # Inside the ''dffButJK'' block, implement a D flip-flop with a JK flip-flop adding only logic gates. |

| − | # Inside the ''dffButT'' block, implement a D flip-flop with a T flip-flop. | + | # Inside the ''dffButT'' block, implement a D flip-flop with a T flip-flop adding only logic gates. |

| − | # Inside the ''dffButSR'' block, implement a D flip-flop with a SR flip-flop. | + | # Inside the ''dffButSR'' block, implement a D flip-flop with a SR flip-flop adding only logic gates. |

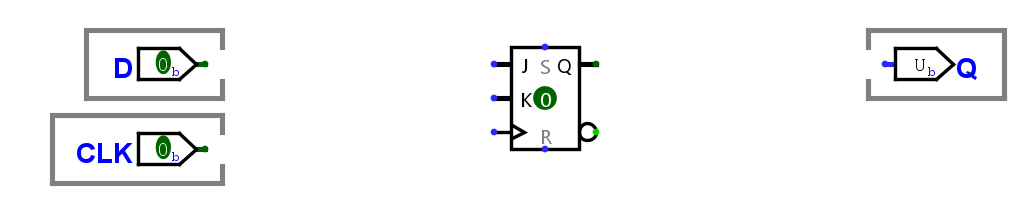

[[File:Eee143lab4template.png|frame|dffButJK block template]] | [[File:Eee143lab4template.png|frame|dffButJK block template]] | ||

Revision as of 15:46, 31 March 2025

Background

In the lectures, we have discussed the different types of flip-flops, as shown in the figure.

Connecting with other classes, flip-flops are more generally considered bistable multivibrators! They have two stable states and can switch between them based on input signals. The only two conditions to become a fully functioning flip-flop useful to implement any synchronous circuit is to be triggerable relative to a clock signal, and to be able to switch states between 1 and 0 (flip-flopping).

The characteristic tables of each flavor is as follows:

| D | Q(t+1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

| J | K | Q(t+1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Q'(t) |

| T | Q(t+1) |

|---|---|

| 0 | Q(t) |

| 1 | Q'(t) |

| S | R | Q(t+1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Undefined/Invalid |

Instructions

Due to the fact that flip-flops only need to be able to switch between 1 and 0 to be able to implement any logic, it is possible to create any flip-flop flavor from any other flip-flop flavor. For this assignment, you are asked to implement D flip-flops using the three other flavors of flip-flops.

- Download the Lab 4 template in UVLe.

- Inside the dffButJK block, implement a D flip-flop with a JK flip-flop adding only logic gates.

- Inside the dffButT block, implement a D flip-flop with a T flip-flop adding only logic gates.

- Inside the dffButSR block, implement a D flip-flop with a SR flip-flop adding only logic gates.

Notes

- Again, do not move any input or output pins in the template.